T-51-10-08

# SP94308 **8-BIT VIDEO SYSTEM ADC**

The Plessey SP94308 analog to digital converter has been specially designed for use with NTSC or PAL video signals. A 1V video signal is AC coupled to the device input, where it is DC clamped, amplified by two and fed through a buffer which drives the ADC input capacitance.

A sync or burst gate pulse can be used to drive the DC clamp circuit. This circuit can be externally adjusted to provide conversion of video only or video and sync.

This analog to digital converter samples the input waveform on the rising edge of the clock and produces a latched output which can be acquired simply by an inverted clock signal.

Also within the SP94308 is an internal clock amplifier and driver. This allows a low level clock signal to be AC coupled directly into the device for applications that may be sensitive to clock radiation.

The clock frequency and analog bandwidth of the SP94308 are compatible with both PAL and NTSC standards where conversion of luma or full composite video signals are required.

#### **FEATURES**

- 8 Bits, 20MHz

- ±0.75 LSB Differential Linearity (Typ.)

- No Sample and Hold or Input Buffer Required

- Internal Clock Amplifier

- Internal Clamp Circuit

- Internal Output Latch

- 6MHz Min. Analog Bandwidth

- Output Levels are TTL/CMOS Compatible

- 0°C to 70°C Temperature Range

- Full Static Protection

- On Chip ×2 Amplifier and ADC Buffer

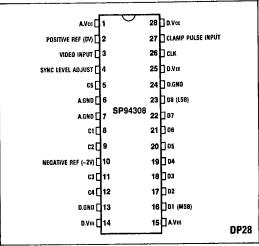

Fig.1 Pin connections - top view

# **ORDERING INFORMATION**

SP94308C DP (Commercial - Plastic DIL package)

#### ABSOLUTE MAXIMUM RATINGS

| Supply voltage Vcc-Vee         | <12V            |

|--------------------------------|-----------------|

| Output current                 | <20mA           |

| Storage temperature            | -65°C to +150°C |

| Junction operating temperature | <150°C          |

### THERMAL INFORMATION

Chip to ambient temperature  $\theta_{JA} = 55$  °C/W

T-51-10-08

ELECTRICAL CHARACTERISTICS Test conditions (unless otherwise stated):  $T_{amb} = 0 ^{\circ}C \ to \ 70 ^{\circ}C, \ Vcc = +5V \pm 0.25V, \ V\epsilon\epsilon = -5.2V \pm 0.25V$

| Characteristic           | Sumb al | Value   |         |      | Unite | Conditions             |

|--------------------------|---------|---------|---------|------|-------|------------------------|

|                          | Symbol  | Min.    | Тур.    | Max. | Units | Conditions             |

| Positive supply current  | Icc     |         | 35      | 44   | mA    |                        |

| Negative supply current  | lee     |         | 110     | 150  | mA    |                        |

| Power consumption        |         |         | 750     |      | mW    |                        |

| Resolution               |         | 8       |         |      | Bits  |                        |

| Reference current        | l ref   |         | 12      | 16   | mA    | V <sub>ref</sub> = -2V |

| Maximum clock rate       | fc      | 20      |         |      | MHz   |                        |

| Clock input level        |         | 0.25    |         | 1.0  | V p-p | AC coupled             |

| Analog bandwidth         | fa      | 6       |         |      | MHz   | Note 3                 |

| Input impedance          | Rin     | 100K    |         |      | Ω     |                        |

| Differential linearity   |         |         | ±0.75   | ±1.0 | LSB   | 25°C                   |

| Integral linearity       | i       |         |         | ±1.0 | LSB   | 25°C                   |

| Differential gain        |         |         |         | 1.5  | %     | fc = 20.0MHz           |

| Differential phase       |         |         | 1       |      | Deg   |                        |

| Logic '1'                | VIH     | Vcc-1.3 | Vcc-1   |      | V     | Isource = 1mA          |

|                          | Vін     | Vcc-1.1 | Vcc-0.9 |      | V     | Isource = 0.1mA        |

| Logic '0'                | Vol     |         | 0.3     | 0.4  | V     | Isink = 1.6mA (Note 2) |

| Tilt/line                |         |         | -1.5    |      | mV    | 100nF input capacitor  |

| Input level              | 1       |         | 1       |      | V p-p | AC coupled             |

| Sync level adjust output | İ       |         | -1.4    |      | V     | Unadjusted (Note 1)    |

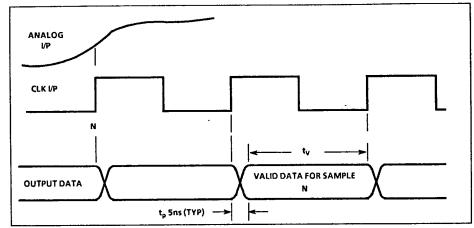

| Data valid time          | tv      |         | 45      |      | ns    | At 20MHz clock         |

#### NOTES

- Gain of x2 in input stage. See Fig.7 for equivalent TTL load. Guaranteed but not tested.

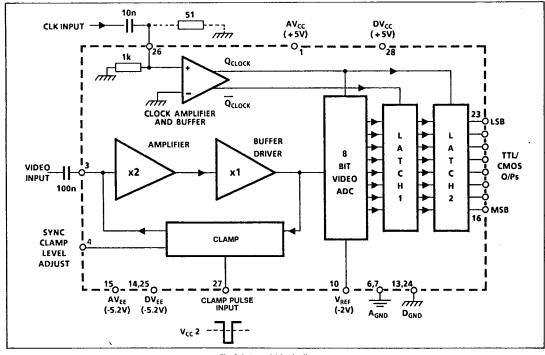

Fig.2 Internal block diagram

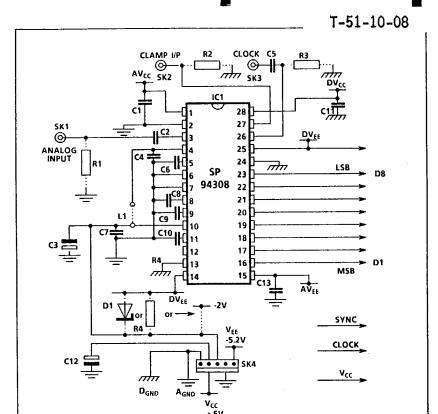

Fig.3 Minimum component application circuit

# **COMPONENT LIST FOR FIG.4**

| Resiste | ors                          | Capac | itors for ADC, clamp, bias etc.       |

|---------|------------------------------|-------|---------------------------------------|

| R1      | 75Ω (optional termination)   | C1    | 100nF (optional decoupling)           |

| R2      | 47Ω (optional termination)   | C2    | 100nF (input coupling and line clamp) |

| R3      | 47Ω (optional termination)   | C3    | 47µF (electrolytic decoupling)        |

| R4      | Approx. 560Ω (optional)      | C4    | 100nF (optional decoupling)           |

|         | Semiconductors               |       | 100nF (coupling)                      |

| Semic   |                              |       | 27pF at 20MHz or 47pF at 10MHz clock  |

| IC1     | SP94308                      | C7    | 100nF (decoupling)                    |

| D1      | BZX79C3V0 (optional)         | C8    | 100nF (decoupling)                    |

|         |                              | C9    | 100nF (decoupling)                    |

| Socke   | ts                           | C10   | 100nF (decoupling)                    |

| S1-S3   | Sub Vis sockets (optional)   | C11   | 100nF (optional decoupling)           |

| S4      | KK Molex socket (optional)   | C12   | 47μF (electrolytic decoupling)        |

| -       | Tit molek dedilet (optional) | C13   | 100nF (optional decoupling)           |

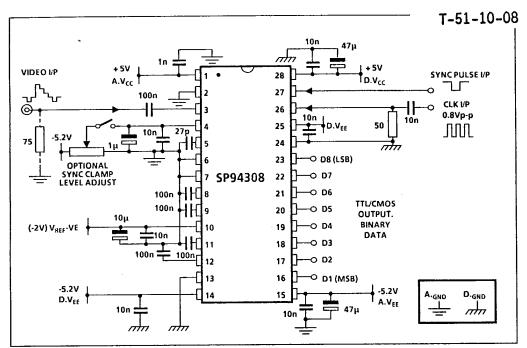

Fig.4 Full test circuit

#### **APPLICATIONS**

The SP94308 combines a clamp circuit, sample and hold, x2 amplifier, ADC driver, video ADC and output latch that form a conventional 8-bit video digitising system.

An on-chip clock amplifier allows the device to be clocked from low level sine or square wave signals. This reduces the possibility of patterning due to crosstalk.

The device offers the flexibility for either sync clamping or black level clamping of the video signal.

#### Sync Clamp

Sync clamping is provided by applying a negative going clamp pulse to pin 27 during the sync period. This pulse should be more than 1.5 µs wide and it should cross the internal switching threshold of Vcc/2. Pin 4 should be connected to VREF- (pin 10 -2V) to allow the total video with its sync to be digitised.

## Black Level Clamping

This can be achieved by applying a negative clamp pulse to pin 27 within the back porch of the video signal. The clamp pulse should avoid the colour burst - this ensures no attenuation of the burst signal.

The clamping pulse can be derived from a burst gate pulse or by delaying the sync pulse with a dual monostable (SN74123N).

When using a back porch clamping pulse, pin 4 should be decoupled to analog ground using a 100nF capacitor. The device will then self-bias this pin to -1.4V. This provides full digitisation of the video and its sync.

It is also possible to adjust the voltage on pin 4 and reduce the reference voltage pin 10 to provide digitisation of the active video information only.

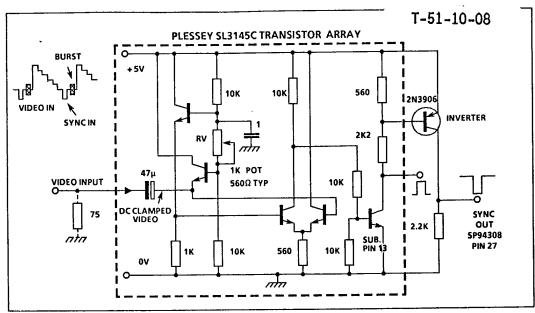

If a clamp pulse is not readily available within the application it can be generated from the incoming video signal (see circuit shown in Fig.5). The variable resistor RV can be adjusted for different slice levels of the incoming video sync

The digital outputs of the SP94308 are latched and have a 90% of CLK, data valid time at 20MHz. This allows the 8-Bit TTL output to be acquired simply by an inverse CLK signal. See Fig.6.

Fig.5 Sync pulse generation for test/evaluation circuit

Fig.6 Timing diagram

Fig.7 Equivalent TTL test load

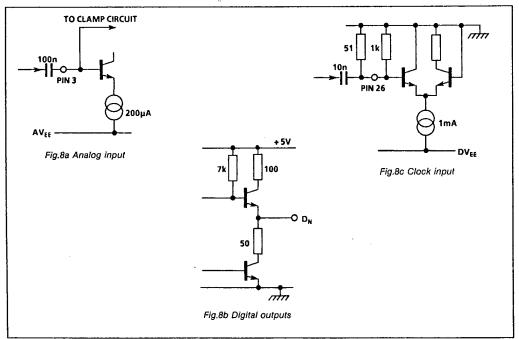

Fig.8 Equivalent device inputs and outputs.