ITT4116 16384-Bit Dynamic Random Access Memory

Rofresh 128 every ZMS

2000

002860

ORIO

NR-CAL ASSOCIATES

PHONE: (415) 961-8121

TWX: (910) 379-6497 1121 SAN ANTONIO ROAD PALO ALTO, CALIF. 94303

#### 16384-Bit Dynamic Random Access Memory

#### **Features**

- Industry standard 16 pin DIP

- 150 ns access time (ITT 4116-2)

- 200 ns access time (ITT 4116-3)

- 250 ns access time (ITT 4116-4)

- All inputs including clocks are TTL compatible

- Standard power supplies, +12V, +5V,

- -5V with  $\pm$  10 % tolerance

- Three state TTL compatible output, Data out is not latched

- Page mode capability

- Addresses and data in have on-chip latches

- Pin and function compatible with Mostek MK 4116

#### General

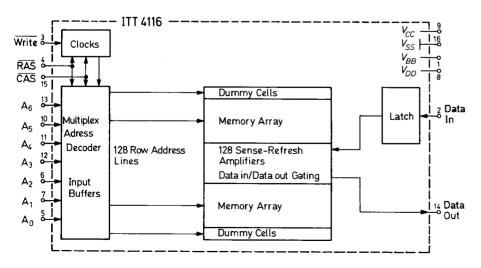

The ITT 4116 is a 16384 word by one bit random access memory fabricated with ITT's N-channel double-poly coplanar silicon gate process for high performance and high functional density. A single transistor dynamic storage cell and dynamic balanced sense amplifiers as used in the ITT 4116 achieve high speed with low power dissipation.

Packaging of the ITT 4116 in the industry standard 16 pin package is made possible by multiplexing the 14 address bits

(required to address 1 of 16384 bits) into the ITT 4116 on 7 address input pins ( $A_0$ - $A_6$ ). Two TTL clocks, row address strobe ( $\overline{(RAS)}$ ) and column address strobe ( $\overline{(CAS)}$ ), latch the two 7 bit address words into the ITT 4116. The 16 pin DIP gives the highest system bit densities and can be handled with widely available automatic testing and insertion equipment.

Several operating modes are incorporated in the ITT 4116 in addition to the usual read and write cycles; read modify write, page mode and  $\overline{RAS}$  only refresh cycles are available.

The ITT 4116 16384 bit memory has the same pin layout as the industry standard ITT 4027 4096 bit memory with the exception of chip select which is replaced by an additional address input needed to accommodate 16384 bits.

# **Absolute Maximum Ratings\***

| Voltage on any pin relative to $V_{BB}$             | . $-0.5 \mathrm{V}\mathrm{to} + 20 \mathrm{V}$ |

|-----------------------------------------------------|------------------------------------------------|

| Voltage on $V_{DD}$ , $V_{CC}$ relative to $V_{SS}$ | 1.0 V to +15 V                                 |

| $V_{BB} - V_{SS}(V_{DD} - V_{SS} > 0)$              | oV                                             |

| Operating temperature, T <sub>A</sub> (Ambient) .   | . 0°C to +70°C                                 |

| Storage temperature (Ambient)                       | ~65 °C to +150 °C                              |

| Short Circuit Output Current                        | 50mA                                           |

| Power dissipation                                   | 1 Watt                                         |

\* Exposure to absolute maximum conditions for extended periods may affect device reliability.

Fig. 1: Block Diagram

# **Package Description**

The ITT 4116 is available in two different package versions:

- in a cerdip 16 pin glass sealed ceramic package, weight approx. 2 g, suffix D to the type number

- in a 16 pin plastic package, weight approx. 1.2 g, suffix N to the type number

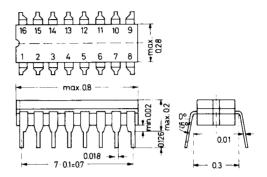

Fig. 2a: Cerdip Package (Suffix D)

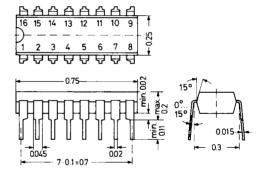

Fig. 2b: Plastic Package (Suffix N)

All Dimensions in inches

# **Pin Connections**

| 1 | Supply Voltage V <sub>BB</sub> | 9  | Supply voltage V <sub>CC</sub> |

|---|--------------------------------|----|--------------------------------|

| 2 | Input Data in                  | 10 | Address input A <sub>5</sub>   |

| 3 | WRITE input                    | 11 | Address input A <sub>4</sub>   |

| 4 | RAS input                      | 12 | Address input A <sub>3</sub>   |

| 5 | Address input A <sub>0</sub>   | 13 | Address input A <sub>6</sub>   |

| 6 | Address input A <sub>2</sub>   | 14 | Output Data out                |

| 7 | Address input A <sub>1</sub>   | 15 | CAS input                      |

| 8 | Supply voltage V <sub>DD</sub> | 16 | Supply voltage V <sub>SS</sub> |

|   |                                |    |                                |

# Recommended DC Operating Conditions $^4$ (0 $^{\circ}C \leqslant T_A \leqslant 70 \,^{\circ}C)^1$

| Parameter                                          | Symbol           | Min.  | Тур. | Max. | Units | Notes |

|----------------------------------------------------|------------------|-------|------|------|-------|-------|

| Supply Voltage                                     | $V_{DD}$         | 10.8  | 12.0 | 13.2 | volts | 2     |

| Supply Voltage                                     | V <sub>cc</sub>  | 4.5 V | 5.0  | 5.5  | volts | 2,3   |

| Supply Voltage                                     | V <sub>SS</sub>  | 0     | 0    | 0    | volts | 2     |

| Supply Voltage                                     | V <sub>BB</sub>  | -4.5  | -5.0 | -5.7 | volts | 2     |

| Logic 1 Voltage, RAS, CAS, WRITE                   | V <sub>IHC</sub> | 2.7   | _    | 7.0  | volts | 2     |

| Logic 1 Voltage, all inputs except RAS, CAS, WRITE | V <sub>IH</sub>  | 2.4   | _    | 7.0  | volts | 2     |

| Logic 0 Voltage, all inputs                        | V <sub>IL</sub>  | -1.0  | _    | 0.8  | volts | 2     |

# $\textbf{DC Electrical Characteristics}^{4} \ (0 \ ^{\circ}\text{C} \leqslant T_{A} \leqslant 70 \ ^{\circ}\text{C})^{1} \ \ (V_{DD} = 12 \ V \ \pm 10\%; \ \ V_{CC} = 5 \ V \ \pm 10\%; \ \ V_{SS} = 0 \ V; \ \ V_{BB} = -4.5 \ V \ to \ -5.7 \ V)$

| Parameter                                                                                   | Symbol           | Min. | Тур.    | Max. | Units | Notes  |  |

|---------------------------------------------------------------------------------------------|------------------|------|---------|------|-------|--------|--|

| Operating Current                                                                           |                  |      |         |      |       |        |  |

| Average power supply operating current                                                      | I <sub>DD1</sub> | _    | - 35 mA |      | mA    | 5      |  |

| $\overline{RAS}$ , $\overline{CAS}$ cycling: $t_{RC} = t_{RC}$ (min)                        | I <sub>CC1</sub> | _    | _       | _    | _     | 6      |  |

|                                                                                             | I <sub>BB1</sub> | -    | _       | 200  | μΑ    | _      |  |

| Standby current                                                                             |                  |      |         |      |       |        |  |

| Power supply standby current                                                                | I <sub>DD2</sub> |      | mA      | 18   |       |        |  |

| $(\overline{RAS} = V_{IHC})$                                                                | I <sub>CC2</sub> | -10  | _       | 10   | μΑ    | _      |  |

|                                                                                             | I <sub>BB2</sub> | -    | _       | 100  | μΑ    | _      |  |

| Refresh Current                                                                             |                  |      |         |      |       |        |  |

| Average power supply current,                                                               | I <sub>DD3</sub> | _    | _       | 27   | mA    | 5, 18  |  |

| refresh mode                                                                                | I <sub>CC3</sub> | -10  | _       | 10   | μΑ    | _      |  |

| $(\overline{RAS} \text{ cycling}, t_{RC} = t_{RC} \text{ (min)}$                            | I <sub>BB3</sub> | -    | _       | 200  | μΑ    | _      |  |

| Page Mode Current                                                                           |                  |      |         |      |       |        |  |

| Average power supply current,                                                               | I <sub>DD4</sub> | -    | _       | 27   | mA    | 5      |  |

| page mode operation                                                                         | I <sub>CC4</sub> | _    | _       | _    | _     | 6      |  |

| $\overline{(RAS)} = V_{IL}, \overline{CAS} \text{ cycling, } t_{PC} = t_{PC} \text{ (min)}$ | I <sub>BB4</sub> | -    | _       | 200  | μΑ    | _      |  |

| Input Leakage Current                                                                       |                  |      |         |      |       |        |  |

| any input ( $V_{BB} = -5 \text{ V}, 0 \text{ V} \leq V_{IN} \leq +7.0 \text{ V},$           | I <sub>IL</sub>  | -10  | -       | 10   | μΑ    | _      |  |

| all other pins not under test = 0 volts)                                                    |                  |      |         |      |       |        |  |

| Output Leakage Current                                                                      | I <sub>OL</sub>  | -10  | _       | 10   | μΑ    | 18, 19 |  |

| Output Levels                                                                               |                  |      |         |      |       |        |  |

| Output high (Logic 1) voltage $(I_{OUT} = -5 \text{ mA})$                                   | V <sub>OH</sub>  | 2.4  | -       | _    | volts | 3      |  |

| Output low (Logic 0) voltage (I <sub>OUT</sub> = 4.2 mA)                                    | V <sub>OL</sub>  | _    | _       | 0.4  | volts | _      |  |

# AC Electrical Characteristics (0 $^{\circ}C \leqslant T_{A} \leqslant 70 \,^{\circ}C)$ (V $_{DD} = 12.0 \, V \pm \, 10\%; \, V_{SS} = 0 \, V; \, V_{BB} = -4.5 \, V$ to $-5.7 \, V)$

| Parameter                                                                                              | Symbol                             | Тур.   | Max.    | Units    | Notes    |

|--------------------------------------------------------------------------------------------------------|------------------------------------|--------|---------|----------|----------|

| Input Capacitance (A <sub>0</sub> –A <sub>6</sub> ), D <sub>IN</sub> Input Capacitance RAS, CAS, WRITE | C <sub>11</sub><br>C <sub>12</sub> | 4<br>8 | 5<br>10 | pF<br>pF | 17<br>17 |

| Output Capacitance (D <sub>OUT</sub> )                                                                 | Co                                 | 5      | 7       | pF       | 17,18    |

# Electrical Characteristics and Recommended AC Operating Conditions (Notes 4, 7, 11)

$(0~^{\circ}C\leqslant T_{A}\leqslant 70~^{\circ}C)^{1}~(V_{DD}=~12.0~V~\pm~10\%;~V_{CC}=5.0~V~\pm~10\%;~V_{SS}=0~V,~V_{BB}=-4.5~V~to~-5.7~V)$

| Parameter                                     | Symbol           | ITT 4116-2 |        | ITT 4116-3 |        | ITT 4116-4 |        |       |       |

|-----------------------------------------------|------------------|------------|--------|------------|--------|------------|--------|-------|-------|

|                                               |                  | Min.       | Max.   | Min.       | Max.   | Min.       | Max.   | Units | Notes |

| Random read or write cycle time               | t <sub>RC</sub>  | 320        | _      | 375        | _      | 410        | -      | ns    | 8     |

| Read write cycle time                         | t <sub>RWC</sub> | 320        | -      | 375        | -      | 425        | _      | ns    | 8     |

| Read modify write cycle time                  | t <sub>RMW</sub> | 320        | -      | 405        | . –    | 500        | _      | _     | -     |

| Page mode cycle time                          | t <sub>PC</sub>  | 170        | -      | 225        | -      | 275        | _      | ns    | -     |

| Access time from RAS                          | t <sub>RAC</sub> | _          | 150    |            | 200    | _          | 250    | ns    | 9,12  |

| Access time from CAS                          | t <sub>CAC</sub> | _          | 100    | _          | 135    | _          | 165    | ns    | 10,1  |

| Output buffer turn-off delay                  | t <sub>OFF</sub> | 0          | 40     | 0          | 50     | 0          | 60     | ns    | 13    |

| Transition time (rise and fall)               | t <sub>⊤</sub>   | 3          | 35     | 3          | 50     | 3          | 50     | ns    | 7     |

| RAS precharge time                            | t <sub>RP</sub>  | 100        | _      | 120        |        | 150        | -      | ns    | -     |

| RAS pulse width                               | t <sub>RAS</sub> | 150        | 10,000 | 200        | 10,000 | 250        | 10,000 | ns    | -     |

| RAS hold time                                 | t <sub>RSH</sub> | 100        | -      | 135        | -      | 165        | -      | ns    | -     |

| CAS hold time                                 | t <sub>CSH</sub> | 150        | -      | 200        | _      | 250        | _      | ns    | -     |

| CAS pulse width                               | t <sub>CAS</sub> | 100        | -      | 135        | _      | 165        | -      | ns    | -     |

| RAS to CAS delay time                         | t <sub>RCD</sub> | 20         | 50     | 25         | 65     | 35         | 85     | ns    | 14    |

| CAS to RAS precharge time                     | t <sub>CRP</sub> | -20        | _      | -20        | _      | -20        | _      | ns    | -     |

| Row Address set-up time                       | t <sub>ASR</sub> | 0          | _      | 0          | -      | 0          | _      | ns    | -     |

| Row Address hold time                         | t <sub>RAH</sub> | 20         | -      | 25         | -      | 35         | -      | ns    | -     |

| Column Address set-up time                    | t <sub>ASC</sub> | -10        | -      | -10        | _      | -10        | -      | ns    | -     |

| Column Address hold time                      | t <sub>CAH</sub> | 45         | -      | 55         | -      | 75         | -      | ns    | -     |

| Column Address hold time referenced to RAS    | t <sub>AR</sub>  | 95         | -      | 120        | _      | 160        | -      | ns    | -     |

| Read command set-up time                      | t <sub>RCS</sub> | 0          | -      | 0          | _      | 0          | -      | ns    | _     |

| Read command hold time                        | t <sub>RCH</sub> | 0          | -      | 0          | -      | 0          | -      | ns    | -     |

| Write command hold time                       | t <sub>WCH</sub> | 45         | -      | 55         | -      | 75         | -      | ns    | -     |

| Write command hold time referenced to RAS     | twcn             | 95         | -      | 120        | -      | 160        | -      | ns    | -     |

| Write command pulse width                     | t <sub>WP</sub>  | 45         | -      | 55         | -      | 75         | -      | ns    | -     |

| Write command to RAS lead time                | t <sub>RWL</sub> | 50         | _      | 70         | -      | 85         | -      | ns    | -     |

| Write command to CAS lead time                | t <sub>CWL</sub> | 50         | -      | 70         | -      | 85         | -      | ns    | -     |

| Data-in set-up time                           | t <sub>DS</sub>  | 0          | -      | 0          | -      | 0          | -      | ns    | 15    |

| Data-in hold time                             | t <sub>DH</sub>  | 45         | -      | 55         | -      | 75         | -      | ns    | 15    |

| Date-in hold time referenced to RAS           | t <sub>DHR</sub> | 95         | -      | 120        | -      | 160        | -      | ns    | -     |

| CAS precharge time (for page-mode cycle only) | t <sub>CP</sub>  | 60         | -      | 80         | -      | 100        | -      | ns    | -     |

| Refresh period                                | t <sub>REF</sub> | -          | 2      | -          | 2      | -          | 2      | ms    | -     |

| WRITE command set-up time                     | t <sub>WCS</sub> | -20        | _      | -20        | -      | -20        | -      | ns    | 16    |

| CAS to WRITE delay                            | t <sub>CWD</sub> | 60         | _      | 80         | -      | 90         | -      | ns    | 16    |

| RAS to WRITE delay                            | t <sub>RWD</sub> | 110        | -      | 145        | _      | 175        | -      | ns    | 16    |

#### Notes

- T<sub>A</sub> is specified for operation at frequencies t<sub>RC</sub> ≥ t<sub>RC</sub> (min).

Operation at higher cycle rates with reduced ambient temperatures and higher power dissipation is permissible provided that all AC parameters are met.

- 2. All voltages referenced to  $V_{\rm SS}$ .

- Output Voltage will swing from V<sub>SS</sub> to V<sub>CC</sub> when enabled, with no current loading. For purposes of maintaining data in standby mode, V<sub>CC</sub> may be reduced to V<sub>SS</sub> without affecting refresh operations or data retention. However, the V<sub>OH</sub> (min) specification is not guaranteed in this mode.

- 4. Several cycles are required after power-up before proper device operation is achieved. Any 8 cycles which perform refresh are adequate for this purpose.

- Current is proportional to cycle rate. I<sub>DD1</sub> (max), I<sub>DD3</sub> (max) and I<sub>DD4</sub> are measured at the cycle rate specified by t<sub>RC</sub> (min).

- 6.  $I_{CC}$  depends on output loading. During readout of high level data  $V_{CC}$  is connected through a low impedance (135  $\Omega$  typ) to Data out. At all other times  $I_{CC}$  consists of leakage currents only.

- V<sub>IHC</sub> (min) or V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IHC</sub> or V<sub>IH</sub> and V<sub>IL</sub>.

- 8. The specifications for  $t_{RC}$  (min) and  $t_{RWC}$  (min) and  $t_{RMW}$  (min) are used only to indicate cycle time at which proper operation over the full temperature range (0 °C  $\leq$  T<sub>A</sub>  $\leq$  70 °C) is assured.

- 9. Assumes that  $t_{RCD} \le t_{RCD}$  (max). If  $t_{RCD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds the value shown.

- 10. Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- 11. AC measurements assume  $t_T = 5$  ns.

- 12. Measured with a load equivalent to 2 TTL loads and 100 pF.

- t<sub>OFF</sub> (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 14. Operation within the t<sub>RCD</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- These parameters are referenced to CAS leading edge in early write cycles and to WRITE leading edge in delayed write or read-modify write cycles.

- 16.  $t_{WCS}$ ,  $t_{WCD}$  and  $t_{RWD}$  are restrictive operating parameters in R·W and RMW cycles only. If  $t_{WCS} \ge t_{WCS}$  (min), the cycle is an early write cycle and the Data Out pin will remain open circuit (high impedance) throughout the entire cycle; if  $t_{CWD} \ge t_{CWD}$  (min) and  $t_{RWD} \ge t_{RWD}$  (min), the cycle is a read-write cycle and the Data Out will contain data read from the selected cell; if neither of the above sets of conditions is satisfied the condition of the Data Out (at access time) is indeterminate.

- 17. Effective capacitance calculated from the equation  $C = \frac{I \cdot \triangle t}{\triangle V}$

with  $\triangle V = 3$  volts and power supplies at nominal levels.

- 18.  $\overline{C A S} = V_{IHC}$  to disable  $D_{OUT}$ .

- 19. 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  + 5.5 V.

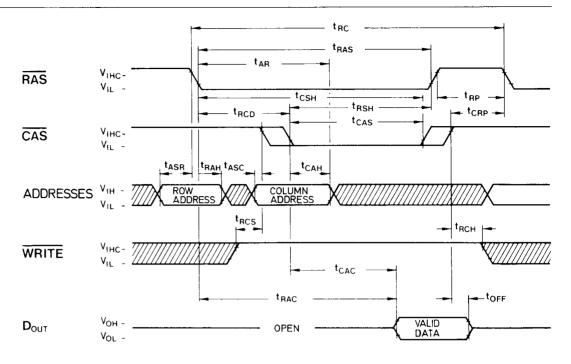

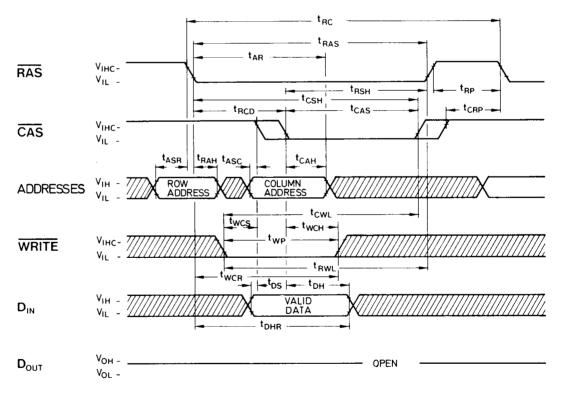

Fig. 3: Read Cycle

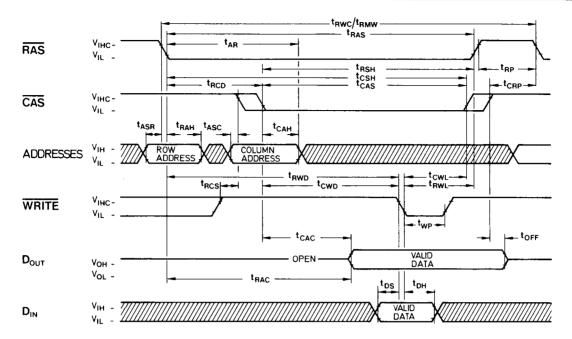

Fig. 4: Write Cycle (Early Write)

Fig. 5: Read-Write/Read-Modify-Write Cycle

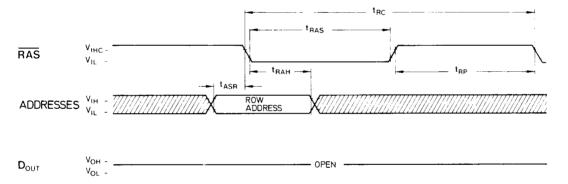

Fig. 6: " $\overline{RAS}$ -Only" Refresh Cycle Note:  $\overline{CAS} = V_{IHC}$ ,  $\overline{WRITE} = Don't Care$

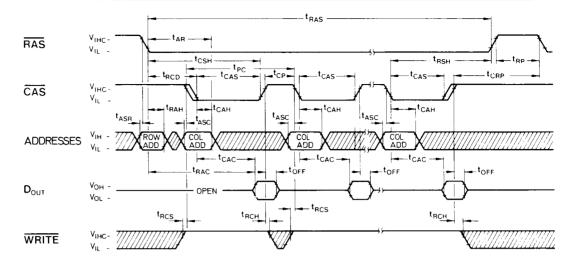

Fig. 7: Page Mode Read Cycle

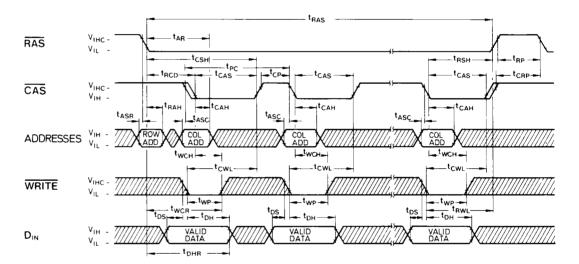

Fig. 8: Page Mode Write Cycle

### Addressing

Fourteen address bits are necessary to decode 1 of the 16384 cell locations and these are multiplexed on to the seven address inputs of the ITT 4116. Two externally applied negative going TTL clock pulses latch these inputs into on-chip address latches. Row Address Strobe (RAS), the first clock, latches the 7 row address bits, and then Column Address Strobe (CAS), the 7 column address bits. An internal clock chain is triggered by RAS and another by CAS; these two logically linked clock chains control the address multiplexing operation so that it occurs outside the critical path timing sequence for read data access. The "gated CAS" feature, that is the internal inhibition of the CAS clock chain until the occurrence of a delayed signal from the RAS clock chain, allows the CAS clock pulse to be applied immediately the Row address information has been changed to Column address information provided the Row Address Hold Time  $(t_{RAH})$  specification has been met. Any delay in applying  $\overline{CAS}$ after t<sub>RAH</sub> will not affect the worst case data access time (t<sub>RAC</sub>) provided CAS occurs before the delayed signal from the RAS clock chain. This window for CAS with no delay in t<sub>BAC</sub> is delineated by two timing endpoints  $t_{BCD}$  (min) and  $t_{BCD}$  (max). If CAS is applied after t<sub>RCD</sub> (max), no data storage or reading errors will result; however, the access time will be determined from CAS access time t<sub>CAC</sub> and therefore t<sub>BAC</sub> will be increased by the amount that the actual t<sub>RCD</sub> exceeds the endpoint t<sub>BCD</sub> (max).

#### Data Input/Output

Input data for an addressed cell is latched into an on-chip register when the three negative clocks  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WRITE}$  are active. The strobe for the Data In (DIN) register is the negative edge of either  $\overline{CAS}$  or  $\overline{WRITE}$ , whichever is the later, thus permitting various write cycle timing options. If the  $\overline{WRITE}$  edge occurs first, DIN is strobed by  $\overline{CAS}$  and set-up and hold times are referenced to  $\overline{CAS}$ . In the case of a readwrite cycle or if the data is not available at  $\overline{CAS}$ , then the DIN is strobed by the delayed  $\overline{WRITE}$  edge and set-up and hold times are referenced to  $\overline{WRITE}$ . "Delayed write" is depicted in the read-write and page mode write cycle timing diagrams and "early write" in the write cycle diagram.

Output of data from an addressed cell is achieved within the specified access time whilst  $\overline{\text{WRITE}}$  is held inactive or high during the period  $\overline{\text{CAS}}$  is active.

### **Data Output Control**

Data Output ( $D_{OUT}$ ) of the ITT 4116 is tri-state TTL compatible and is normally high impedance (i.e. open-circuit and floating). During a read cycle, the output will turn on to either logic 1 or logic 0 at the access time when  $\overline{CAS}$  is activated (low level). The valid output data will remain until  $\overline{CAS}$  is taken high.

In the case of a read, read-modify-write, or delayed write cycle,  $D_{OUT}$  contains the data read from the addressed cell after the access time; this data is the same polarity (not inverted) as the input data. Having gone active the validity of data until  $\overline{CAS}$  goes high is unaffected by the subsequent state of  $\overline{RAS}$ .

If the cycle is "early write" ( $\overline{WRITE}$  active before  $\overline{CAS}$ ) then  $D_{OUT}$  remains in the high impedance state throughout the cycle. The effect of this mode of operation is that the user can control the data output by the position of the  $\overline{WRITE}$  edge during a write cycle and the pulse width of  $\overline{CAS}$  during read.

Output control of this nature results in important system operations:

#### Common I/O operation:

D<sub>IN</sub> can be connected directly to D<sub>OUT</sub> giving a common I/O data bus, provided all write operations are in the "early write" mode.

# Data Output Control:

$\frac{D_{OUT}}{CAS}$  goes inactive, this allows data to remain valid until the beginning of a subsequent cycle without increasing overall memory cycle time. Thus flexible  $\overline{RAS}$  /  $\overline{CAS}$  timing relationships are possible.

# Chip Selection:

As D<sub>OUT</sub> is not latched,  $\overline{CAS}$  is not required to turn off the outputs of unselected devices. Two methods of chip select are possible by decoding  $\overline{CAS}$  and/or  $\overline{RAS}$ . If both are decoded then a two dimensional chip select array is possible.

#### Extended Page Boundary:

In page mode operation, multiple column locations are accessed using the same row address in successive memory cycles. If  $\overline{CAS}$  is decoded as a page cycle select signal, the page boundary can be extended beyond the 128 column locations of an individual chip.

# **Output Interfacing**

The data output buffer has a low impedance to V<sub>CC</sub>, 420  $\Omega$  maximum (135  $\Omega$  typically), for logic state "1" and a low impedance to V<sub>SS</sub>, 95  $\Omega$  maximum (35  $\Omega$  typically), for logic state "0". Power to the output buffer can be supplied at the supply voltage of interfacing chips using the separate V<sub>CC</sub> pin. In standby battery operation, refresh operation of the ITT 4116 is unaffected by removal of power to this separate V<sub>CC</sub>, thus all system logic except  $\overline{RAS}$  timing circuitry and the refresh address logic may be turned off, minimising power requirements.

# **Page Mode Operation**

Multiple column locations may be accessed using the same row address in successive memory cycles; this page mode of operation of the ITT 4116 gives increased speed without increased power. Power is reduced as the RAS is kept active (logic "0") after the initial strobe on the first cycle so eliminating the power required on the negative edge of RAS. Additionally, access and cycle times are reduced by the elimination of time required for strobing the new row.

A single ITT 4116 limits the page boundary to the 128 columns available; however, when more than 16K words are used in a system, the use of  $\overline{CAS}$  as a chip select signal extends the page boundary.  $\overline{RAS}$  is applied to all devices and  $\overline{CAS}$  is decoded as a page cycle select signal: only those devices receiving both  $\overline{RAS}$  and  $\overline{CAS}$  will perform memory cycles.

#### Refresh

The dynamic cell matrix requires refresh within every 2 milliseconds at each of the 128 row addresses. Although any memory cycle will achieve this refresh, substantial power savings can easily be made by using  $\overline{RAS}$ -only cycles as can be seen from the  $I_{DD3}$  specification.

#### **Power Considerations**

The ITT 4116 consists mainly of dynamic circuitry and most power is consumed on address strobe edges. Power, therefore, is a function of operating frequency rather than active duty cycle (see Fig. 5). Additionally destruction of the device will not result from the clock inputs accidentally becoming grounded.

Provided supply voltages are within specification, no special power noise restrictions are necessary, although adequate decoupling should be provided to suppress high frequency transients to ensure optimum reliability and system performance. As the ITT 4116 draws very little DC power there is minimal need for large capacitors.

For systems requiring low power dissipation, it is necessary to reduce the operation frequency. For example, if the cycle time is 1 microsecond, the operating current will be 20 mA maximum rather than the 35 mA for 375 ns cycle time. Conversely it may be possible for some ITT 4116 to operate with shorter cycle times than 375 ns, provided all AC requirements are met; however, the increased power dissipation will require a reduction in ambient temperature.

Minimum overall system power requirements are achieved if  $\overline{RAS}$  as opposed to  $\overline{CAS}$  is used to chip select as unselected devices then are in low power (standby) mode regardless of  $\overline{CAS}$ .

#### Power Up

The ITT 4116 requires no particular power supply sequencing so long as the Absolute Maximum Rating Conditions are observed. However, in order to ensure compliance with the Absolute Maximum Ratings, ITT recommends sequencing of power supplies such that  $V_{BB}$  is applied first and removed last.  $V_{BB}$  should never be more positive than  $V_{SS}$  when power is applied to  $V_{DD}.$

Under system failure conditions in which one or more supplies exceed the specified limits significant additional margin against catastrophic device failure may be achieved by forcing RAS and Data Out to the inactive state.

After power is applied to the device, the ITT 4116 requires several cycles before proper device operation is achieved. Any 8 cycles which perform refresh are adequate for this purpose.

# Production and Marketing Centers:

# U. S. A.:

ITT Semiconductors 500, Broadway, Lawrence, Mass. 01841 Tel. 617-688-1881 TWX 710-342-1357

#### U. K.:

ITT Semiconductors Maidstone Road Sidcup DA14 5HT, Kent Tel. (01) 300 3333 Telex 21836

# W. Germany:

INTERMETALL GmbH P. O. Box 840 D-7800 Freiburg Tel. (761) 5171 Telex 7-72715

#### Japan:

ITT Semiconductors P. O. Box 21 Shinjuku-ku Tokyo 160-91 Tel. 3478881-5 Telex 22858

Reprinting is generally permitted, indicating the source. However, our consent must be obtained in all cases. Information furnished by ITT is believed to be accurate and reliable. However, no responsibility is assumed by ITT for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of ITT. The information and suggestions are given without obligation and cannot give rise to any liability; they do not indicate the availability of the components mentioned. Delivery of development samples does not imply any obligation of ITT to supply larger amounts of such units to a fixed term. To this effect, only written confirmation of orders will be binding.

Printed in W.-Germany · Imprimé dans la République Fédérale d'Allemagne by Druckhaus Rombach+Co GmbH, 7800 Freiburg

Edition 1980/5 · Order No. 6251-121-5E