SOME INFORMATION ON THE MTX THAT I WISH I'D HAD IN THE 1980'S....

## 0 CONTENTS

| 1 | Intr | oduction                                                  | 4  |

|---|------|-----------------------------------------------------------|----|

| 2 | Und  | der the hood                                              | 5  |

| 3 | The  | Memory Map                                                | 7  |

|   | 3.1  | Rom Enabled Mode                                          | 7  |

|   | 3.2  | CPM Mode                                                  | 9  |

|   | 3.3  | The 256k Series 2                                         | 10 |

|   | 3.4  | Using Paged Memory                                        | 11 |

| 4 | The  | e Video System                                            | 13 |

|   | 4.1  | Accessing the Display via RST 10 and RST 28               | 13 |

|   | 4.2  | Accessing the VDP directly                                | 17 |

|   | 4.3  | Text Mode                                                 | 20 |

|   | 4.4  | Graphics 2 Mode                                           | 23 |

|   | 4.4. | .1 Graphics 2 in text mode                                | 26 |

| 5 | The  | 2 CTC                                                     | 28 |

|   | 5.1  | 125hz Interrupt                                           | 29 |

|   | 5.1. | .1 So why 125Hz?                                          | 30 |

|   | 5.1. | .2 MTX BASIC and Interrupts                               | 30 |

|   | 5.2  | Baud Rate Clocks                                          | 30 |

|   | 5.3  | VDP interrupt                                             | 31 |

|   | 5.4  | Interrupt priority                                        | 31 |

| 6 | The  | PSG                                                       | 33 |

|   | 6.1  | PSG registers                                             | 33 |

|   | 6.2  | Driving the PSG                                           | 34 |

| 7 | The  | e keyboard                                                | 37 |

|   | 7.1  | Reset keys                                                | 37 |

|   | 7.2  | The main keyboard                                         | 37 |

| 8 | Ехр  | pansion Potential                                         | 40 |

|   | 8.1  | Connector layout                                          | 41 |

|   | 8.2  | Connecting a ROMpak or external 8k (E)EPROM               | 41 |

|   | 8.3  | Connecting RAM to the external connector                  | 42 |

|   | 8.4  | Connecting Input/Output devices to the External connector | 44 |

| 9 | Projects |                        | 47  |

|---|----------|------------------------|-----|

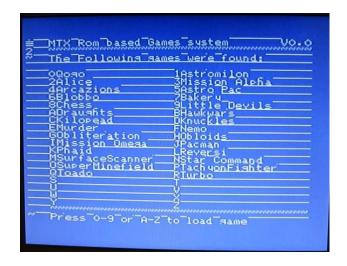

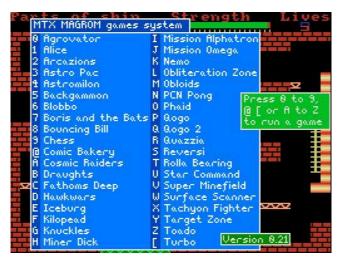

|   | 9.1 Ma   | grom                   | 47  |

|   | 9.1.1    | Magrom Software        | 48  |

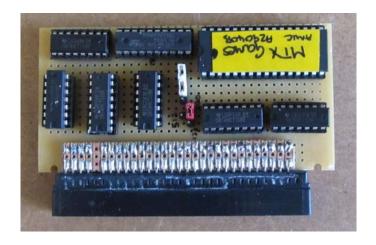

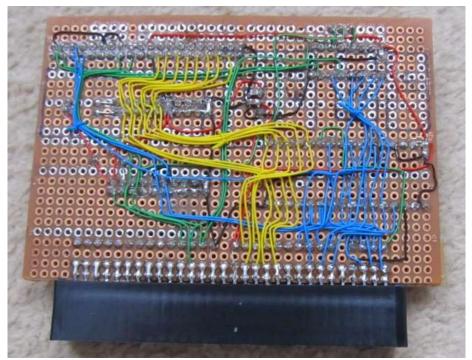

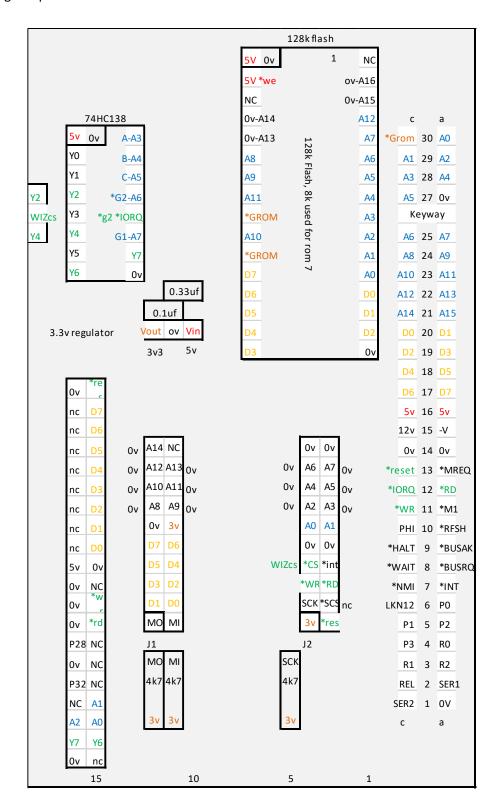

|   | 9.1.2    | The Magrom Hardware    | 58  |

|   | 9.2 CFX  | <                      | 61  |

|   | 9.2.1    | CFX IDE Software       | 61  |

|   | 9.2.2    | CFX Support Software   | 76  |

|   | 9.2.3    | CFX CPM Screen Driver  | 91  |

|   | 9.2.4    | CFX Hardware           | 113 |

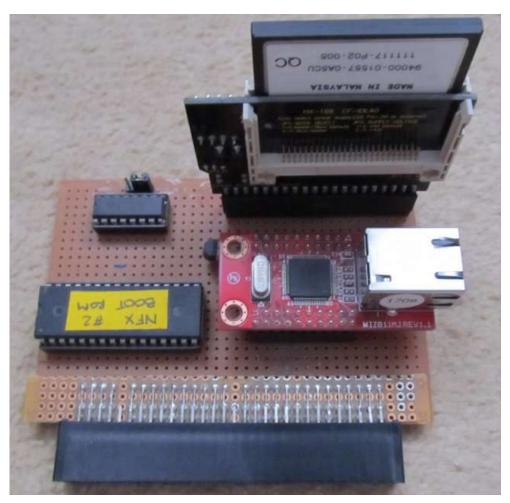

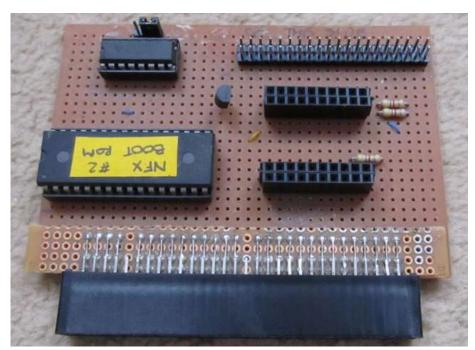

|   | 9.3 NF   | <                      | 117 |

|   | 9.3.1    | NFX Hardware           | 117 |

|   | 9.3.2    | NFX IDE support        | 121 |

|   | 9.3.3    | NFX CPM screen driver. | 125 |

## 1 Introduction

Over its lifetime the MTX was supplied with 2 different manuals, the original one was adequate, but only just. It suffered a little in that although there was an introduction to BASIC and Noddy, and a technical section at the back with lots of info on the hardware and component parts, there wasn't a lot in between the two.

The 2<sup>nd</sup> manual had a lot more useful detail for the BASIC programmer but was still short of covering the gap between BASIC and the technical appendices.

So back in 1987 Keith Hook wrote a book called "The Source" about some of the more technical aspects of the MTX series of computers, to bridge the gap between the sections in the manual(s).

While it may not be the best book ever written, it is one of the few available for the MTX. During the development of the MTX plus project with Dave Stevenson, Dave provided me with a copy of the book. I found some information of use for the project, I also found some of the information to be presented in a confusing manner, of in a couple of spots just plain wrong.

This therefore is my attempt at correcting some of the errors and presenting things in a way that makes more sense to me. I assume that anyone reading this has at least a basic Knowledge of the MTX and the Z80 CPU.

I'd like to thank Andy Key for adding the screen dump facility in to Memu, and Dave Stevenson for reading the first draft and his many useful suggestions.

## 2 UNDER THE HOOD

The MTX series of computes were designed using "Off the Shelf" products available in the early 1980's the major components of the design were

4mhz Z80A CPU

4mhz Z80A CTC

TMS9929A VDP

**SN76489A PSG**

4MHz Z80 DART - available on the optional RS232 expansion

Memory varied between systems from 32k on the MTX500, up to a theoretical maximum of 784k available as paged memory under CPM. This was supplied as dynamic RAM which was the norm for the time. For the early systems ram was 64k by 1-bit chips later designs used 256k by 1-bit parts. At the time memory chip manufacturers would package "failed" 64k chips where one of the two 32k banks within the device was working as 32k chips and Memotech used these on the MTX500 and the 32k RAM card.

The motherboard has a system of links between the CPU and the RAM to accommodate either high or low bank 32k RAMs on the MTX500 along with a setting for 64 or 32k on board to identify to the memory configuration PAL (Programable Address Logic) whether the system was the MTX500 or MTX512. The RAM expansion card would also have a PAL programmed to the specific type of RAM fitted to the card and for the system it was to be plugged in to.

The 256k MTX series 2 used the larger 256k devices and along with a re-designed PAL needed patch wiring on the reverse side of the board to make them fit.

The 24k of operating system on the MTX, in common with other systems of the era, isn't anything like what would be considered one today. Rather there is a collection of routines needed to support MTX BASIC. It's evident from the ROM listing and the state of the error messages, that the programmers were struggling to fit everything they wanted into the space available.

Some parts of the system are written to use a common access point, for other parts however, it's up to the user to discover "useful" sections within the ROM and call them directly. This then raises potential issues to anyone that wants to modify the ROM contents, for example removing some of the foreign language tables in order to fix the error massages, as software that relies on those entry points would fail.

The majority of the components on the board were standard 74LS series logic. These provided the "ports" for memory mapping, the keyboard and Joysticks, the printer and cassette tape.

The VDP was fitted with 16k of its own dedicated video memory, which was the maximum the device would accept. These used 3 voltage 16k by 1-bit RAM chips which have proved to be a reliability problem as the systems age.

Storage on the basic system was to cassette tape only. There were 2 different floppy disc systems available from Memotech during the life of the MTX.

The FDX was a large system that could accommodate 2 5.25" drives within the chassis and further external 5.25" or 8" if required. The FDX required 64k of RAM to operate as it was essentially a CPM system. An 80 column video card was a standard part of the CPM system, allowing the use of dual monitors for developing programs. A supplied program, FDXB.COM, enabled access to MTX BASIC with 32k of RAM available like the MTX500. The on-board card frame would also accept solid state "silicon discs" under CPM for additional high speed, temporary storage.

The SDX expansion, at least initially, didn't offer CPM, instead it had an expansion ROM which added a number of commands to MTX BASIC. The underlying disc system however was CPM, allowing the interchange of discs between the FDX and SDX. Later SDX systems had an extra paged ROM on board that allowed CPM in addition to the BASIC extensions. Some also had extra RAM available as a RAM disc, echoing the silicon discs of the FDX.

## 3 THE MEMORY MAP

The MTX memory map is complex, in order to fit the operating sys and a reasonable amount of memory into the 64k available to a Z80, a memory paging system is used. To make things more complicated, CPM requires another totally different memory layout in order to function.

Memotech assigned the Z80 output port 0 as a write only memory configuration register. Since the port is write only, they also added a system variable PAGE at #FAD2 (64210 decimal) to store a copy of the current memory configuration.

The Z80's 64k memory is split into 4 logical blocks each 16k in size. In ROM mode the first 16k block, #0000 to #3FFF, is allocated to system ROM, the next 2 blocks at #4000 to #7FFF and #8000 to #BFFF are paged RAM. In the MTX500 the lower of those 2 blocks is empty.

In CPM mode, there is no ROM, so all 3 of these blocks are allocated to paged RAM. In large memory systems, this results in each 16k block of RAM within the paging system potentially having 2 different locations.

The final 16k, occupying the area between #C000 and #FFFF is fixed, and always available to the CPU in either mode. It is home to those parts of the system that must be available to the CPU at all times.

As the Z80 is an 8-bit CPU, there are 8 bits available in any memory or I/O port. The paging register is split into 3 sections.

The 4 lowest bits, labelled P0, P1, P2 & P3 select which of the available RAM pages will be accessed making a maximum of 16 pages available in either mode. In RAM mode this is 16 pages 48k in size, in ROM mode it is 16 pages of 32k. The next 3 bits designated as R0, R1 & R2 select the current paged ROM from a total of 8.

The final bit, RELCPMH, determines whether the system has the ROMs enabled, or is in RAM only CPM mode. The name apparently stands for Rom Enabled Low CPM High

#### 3.1 ROM ENABLED MODE

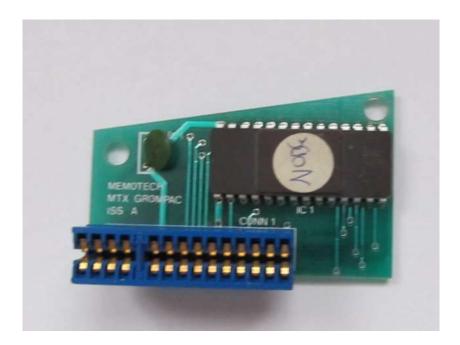

ROM mode is set when the RELCPMH bit is set to a 0. As noted before, the standard MTX has 24k of onboard ROM, in order to fit this into the 16k space allowed for ROMs, Memotech decided to page the upper 8k, leaving the lower 8k fixed. Since there are 3 bits allocated to the ROM paging system this enabled a total of 72k ROM to be fitted. (9 x 8k ROMSs, 8 paged, 1 fixed) The hardware on the motherboard decodes the lower 8k ROM and paged ROMs 0,1 and 7.

ROM 7 isn't used by the motherboard, but this signal is instead made available on the expansion connector for use by external hardware, and is intended for the ROMpak or NODE ROM.

The lower 8k ROM and paged ROMs 0 and 1 then make up the 24k of the operating system. Typically, ROM 4 would be used by CPM, and ROM 5 by the SDX ROM, although some SDX systems used ROM slot 3.

The internal ROM expansions (NewWord, Pascal and the video wall software) used ROM page 2, which because of additional hardware on the expansion card could be sub paged into up to 256 ROM pages.

The MTX 500 has 32k of available RAM, since half of this is fixed by design as occupying the top 16K of the memory map. Memotech made the obvious decision to fit the other 16k directly below to maintain a continuous 32k block of memory, this 16k is in RAM page 0. The 16k between the top of the ROM and the bottom of the RAM is then empty, any attempt to "poke" data into this area will result in the data being lost, "peeking" from this area will return garbage.

| MTX50 | MTX500 memory map |                |               |               |                |  |  |  |  |

|-------|-------------------|----------------|---------------|---------------|----------------|--|--|--|--|

| Page  | #0000 to #1FFF    | #2000 to #3FFF | #4000 - #7FFF | #8000 - #BFFF | #C000 - #FFFFF |  |  |  |  |

| 0     | OS ROM            | BASIC ROM      | Empty         | 16k paged RAM | 16k Shared RAM |  |  |  |  |

| 1     |                   | Assem ROM      |               | Empty         |                |  |  |  |  |

| 2     |                   | Expansion      |               |               |                |  |  |  |  |

| 3     |                   | Expansion      |               |               |                |  |  |  |  |

| 4     |                   | DISC (CPM)     |               |               |                |  |  |  |  |

| 5     |                   | DISC (SDX)     |               |               |                |  |  |  |  |

| 6     |                   | Expansion      |               |               |                |  |  |  |  |

| 7     |                   | ROMpak         |               |               |                |  |  |  |  |

| 8-15  | N/A               | _              |               |               |                |  |  |  |  |

The MTX512 on the other hand has 64k of RAM available, however there is only 48k in the memory map allocated to RAM, the extra 16k has to go into page 1 due to the limitations of the PAL that controls the motherboard memory paging, the extra 16k has to occupy the area from #8000 to #BFFF in page 1, this also makes for a continuous 32k block being available in page 1 as the paged RAM adjoins the 16k fixed area.

| MTX51 | MTX512 memory map |                |               |               |                |  |  |  |  |  |

|-------|-------------------|----------------|---------------|---------------|----------------|--|--|--|--|--|

| Page  | #0000 to #1FFF    | #2000 to #3FFF | #4000 - #7FFF | #8000 - #BFFF | #C000 - #FFFFF |  |  |  |  |  |

| 0     | OS ROM            | BASIC ROM      | 16k Paged RAM | 16k paged RAM | 16k Shared RAM |  |  |  |  |  |

| 1     |                   | Assem ROM      | Empty         | 16k Paged RAM |                |  |  |  |  |  |

| 2     |                   | Expansion      |               | Empty         |                |  |  |  |  |  |

| 3     |                   | Expansion      |               |               |                |  |  |  |  |  |

| 4     |                   | DISC (CPM)     |               |               |                |  |  |  |  |  |

| 5     |                   | DISC (SDX)     |               |               |                |  |  |  |  |  |

| 6     |                   | Expansion      |               |               |                |  |  |  |  |  |

| 7     |                   | ROMpak         |               |               |                |  |  |  |  |  |

| 8-15  | N/A               |                |               |               |                |  |  |  |  |  |

Adding RAM to either system is done in multiples of 32k. A MTX512, with an additional 128k would have the memory arranged so that the 5 lowest pages were full, and a 6<sup>th</sup> half full page would be filled from the top. Page 244 of the Phoenix manual has this wrong, though the equivalent table in the original manual was correct.

| MTX51 | MTX512 with 128k expansion |                |               |               |                |  |  |  |  |

|-------|----------------------------|----------------|---------------|---------------|----------------|--|--|--|--|

| Page  | #0000 to #1FFF             | #2000 to #3FFF | #4000 - #7FFF | #8000 - #BFFF | #C000 - #FFFFF |  |  |  |  |

| 0     | OS ROM                     | BASIC ROM      | 16k Paged RAM | 16k paged RAM | 16k Shared RAM |  |  |  |  |

| 1     |                            | ASSEM ROM      | 128k exp. (a) | 16k Paged RAM |                |  |  |  |  |

| 2     |                            | Expansion      | 128k exp. (c) | 128k exp. (b) |                |  |  |  |  |

| 3     |                            | Expansion      | 128k exp. (e) | 128k exp. (d) |                |  |  |  |  |

| 4     |                            | DISC (CPM)     | 128k exp. (g) | 128k exp. (f) |                |  |  |  |  |

| 5     |                            | DISC (SDX)     | Empty         | 128k exp. (h) |                |  |  |  |  |

| 6     |                            | Expansion      |               | Empty         |                |  |  |  |  |

| 7     |                            | ROMpak         |               |               |                |  |  |  |  |

| 8-15  | N/A                        |                |               |               |                |  |  |  |  |

During start up, the MTX ROM does a very simple check for available paged RAM, and stores the result in the system variable LSTPG at #FA7A (64122 decimal). PRINT PEEK (64122) returns the number of 32k pages of RAM - 1; the MTX500 will return 0, a standard MTX512 returns a 1. The example MTX 512 + 128k above would return 5.

Anyone using an MTX fitted with Andy Key's REMEMOorizer will get a result of 11, indicating there is  $384k (32k \times 11 + 32k)$  available from BASIC.

## 3.2 CPM Mode

Setting CPM mode on an MTX500 is possible, but serves no purpose, as all it does is page out the ROMs, however as there is no additional RAM in the system this just serves to create a vacant 32k block in lower memory.

The 64k in the MTX512 is the minimum required for CPM, with the RELCPMH bit set to 1 all 64k RAM is available in page 0, the other pages are empty. Leaving the memory map looking like this:

| MTX51 | 12 RAM only memory map |               |               |                |  |  |  |  |  |  |

|-------|------------------------|---------------|---------------|----------------|--|--|--|--|--|--|

| Page  | #0000 to #3FFF         | #4000 - #7FFF | #8000 - #BFFF | #C000 - #FFFFF |  |  |  |  |  |  |

| 0     | 16 k Paged RAM         | 16k Paged RAM | 16k paged RAM | 16k Shared RAM |  |  |  |  |  |  |

| 1     | Empty                  | Empty         | Empty         |                |  |  |  |  |  |  |

| 2     |                        |               |               |                |  |  |  |  |  |  |

| 3     |                        |               |               |                |  |  |  |  |  |  |

| 4-15  |                        |               |               |                |  |  |  |  |  |  |

Note that the lighter shaded page has "moved", in ROM mode it's in page 1 at #8000, in CPM mode it's the very first block in page 0. This moving page only occurs on systems using memory based on the 64k RAM chip, the MTX series 2 using the larger 256k chips is unable to duplicate this behaviour due to the limitations of the 14L4 PAL used by Memotech.

Expansion memory starts in page 1 and grows upward from the lowest point in memory, depending on the amount of RAM fitted, the final page could have a gap in the map between the last block of RAM

fitted and the shared RAM at #C000. The example below as taken from the manual of a MTX512 with an extra 128k illustrates this, Page 3 has memory available in the lowest 32k and the top 16k, however the area from #8000 to #BFFF is empty. It's worth noting that every one of the blocks has moved from the position it had in RAM mode. For example, block e which was in page 3 at #4000 is now in page 2 at the same address. Block a is still in page 1 but has moved from #4000 to #0000

| MTX51 | MTX512 RAM only memory map with 128k expansion |               |                |                |  |  |  |  |  |  |

|-------|------------------------------------------------|---------------|----------------|----------------|--|--|--|--|--|--|

| Page  | #0000 to #3FFF                                 | #4000 - #7FFF | #C000 - #FFFFF |                |  |  |  |  |  |  |

| 0     | 16 k Paged RAM                                 | 16k Paged RAM | 16k paged RAM  | 16k Shared RAM |  |  |  |  |  |  |

| 1     | 128k exp. (a)                                  | 128k exp. (b) | 128k exp. (c)  |                |  |  |  |  |  |  |

| 2     | 128k exp. (d)                                  | 128k exp. (e) | 128k exp. (f)  |                |  |  |  |  |  |  |

| 3     | 128k exp. (g)                                  | 128k exp. (h) | Empty          |                |  |  |  |  |  |  |

| 4-15  | Empty                                          | Empty         |                |                |  |  |  |  |  |  |

## 3.3 THE 256k SERIES 2

The MTX512 series 2 was fitted with 256k by 1-bit RAM chips, however restrictions imposed by the motherboard and the memory PAL meant that not all of that RAM was accessible in either mode. It also meant the moving page from the earlier systems could not be duplicated.

The RAM itself was mapped into the first 4 pages. Any portions that aren't obscured by the ROM or shared RAM are visible to the CPU.

| MTX51 | MTX512 Series 2 |                |               |               |                |  |  |  |  |  |

|-------|-----------------|----------------|---------------|---------------|----------------|--|--|--|--|--|

| Page  | #0000 to #1FFF  | #2000 to #3FFF | #4000 - #7FFF | #8000 - #BFFF | #C000 - #FFFFF |  |  |  |  |  |

| 0     | OS ROM          | BASIC ROM      | 16k Paged RAM | 16k paged RAM | 16k Shared RAM |  |  |  |  |  |

| 1     |                 | Assem ROM      | 16k Paged RAM | 16k paged RAM |                |  |  |  |  |  |

| 2     |                 | Expansion      | 16k Paged RAM | 16k paged RAM |                |  |  |  |  |  |

| 3     |                 | Expansion      | 16k Paged RAM | 16k paged RAM |                |  |  |  |  |  |

| 4     |                 | DISC (CPM)     | Empty         | Empty         |                |  |  |  |  |  |

| 5     |                 | DISC (SDX)     |               |               |                |  |  |  |  |  |

| 6     |                 | Expansion      |               |               |                |  |  |  |  |  |

| 7     |                 | ROMpak         |               |               |                |  |  |  |  |  |

| 8-15  | N/A             |                |               |               |                |  |  |  |  |  |

With RELCPMH set to 1, the 4 banks of RAM that were previously covered by the ROM are now visible

| MTX51 | 12 Series 2 RAM only mode |               |                             |                |  |  |  |  |  |

|-------|---------------------------|---------------|-----------------------------|----------------|--|--|--|--|--|

| Page  | #0000 to #3FFF            | #4000 - #7FFF | #8000 - #BFFF               | #C000 - #FFFFF |  |  |  |  |  |

| 0     | 16k paged RAM             | 16k Paged RAM | 16k paged RAM               | 16k Shared RAM |  |  |  |  |  |

| 1     | 16k paged RAM             | 16k paged RAM | 16k paged RAM               |                |  |  |  |  |  |

| 2     | 16k paged RAM             | 16k paged RAM | 16k paged RAM               |                |  |  |  |  |  |

| 3     | 16k paged RAM             | 16k paged RAM | 16k paged RAM 16k paged RAM |                |  |  |  |  |  |

| 4-15  | Empty                     | Empty         | Empty                       |                |  |  |  |  |  |

#### 3.4 Using Paged Memory

There are 2 things to be aware of when using the page port:

the first is not to move a page that the CPU is currently using, and

the other is to take precautions for interrupts.

For safety, on start-up, the MTX ROM initializes the Z80's stack pointer to use shared RAM at #FD48. If the system stack were placed in paged RAM, then a system crash would be the likely result of any RAM re-paging. The OS takes care to only re-map the paged ROMs while running from the fixed OS ROM, likewise a user program changing the RAM page should only do so with code that is running in the shared RAM area.

If a paged ROM needs to access routines in another paged ROM, then it needs to do the same as the SDX ROM, copy a short routine into RAM that changes the ROM page and calls the appropriate routine then reverts to the original set up before returning.

When running in BASIC, the MTX interrupt system generates 125 interrupts per second, which needs to be serviced and may or may not involve a different paged ROM. On exit from the interrupt, the system checks PAGE and uses that to reset the memory map to its original setting before returning. Therefore, the following code should be used when changing pages:

```

LD (PAGE), A OUT (#00), A

```

The system variable needs to be changed first, otherwise an interrupt occurring between the 2 instructions could leave the page port in an incorrect state. With the instructions this way around, if an interrupt were to split them, then the only result would be that the memory would already be remapped making the OUT instruction redundant.

For relatively short sequences of code, it's also possible to disable interrupts while paging, though that's not really recommended.

As a practical example, the MTX has 24k of ROM, it's possible to use PEEK from BASIC to examine the lower 8k of ROM, it's also possible to read one of the 2 paged ROMs, but not the other. You can only PEEK the ROM that the PEEK command itself runs from. The same issue arises with PANEL, the only paged ROM that can be examined is the one that PANEL occupies. Should you want to examine the contents of one of the other paged ROMs they need copying to RAM first.

The following program would copy the contents of ROM 2 to #A000, should you want to examine another ROM, just change #4019 to LD A,#30 or #40 etc. the first digit is the ROM number from 0 to 7, the last digit should be a 0 to ensure the copy goes to accessible RAM, using hex numbers in this instance make the intention clearer.

NB While the MTX's built in assembler is functional and reasonably fast, it lacks a decent equates system, so it's not always possible to avoid using numerical references where a label would be clearer. E.g. It is not possible to set a label for PAGE, instead #FAD2 has to be used. The original manual's assembler and panel section is pretty abysmal. The later manual is much better in that respect, but still not great.

```

10 ASSEM

CODE

4007

LD DE, #D000

400A

LD BC, #20

400D

LD HL, START

4010

LDIR

4012

JP #D000

4015 START: LD A, (#FAD2)

4018

PUSH AF

LD A, #20

4019

401B

LD (#FAD2),A

401E

OUT A, (0)

4020

LD HL, #2000

4023

LD DE, #A000

4026

LD BC, #2000

4029

LDIR

402B

POP AF

402C

LD (#FAD2),A

402F

OUT A, (0)

4031

RET

Symbols:

4015

START

```

The first 4 lines used the Z80 block move to copy the actual code into shared RAM, which is then run by the JP instruction on the 5<sup>th</sup> line.

Since this code is designed to only change the paged ROM, and as a user program is running in RAM page 0, copying the code to shared RAM first isn't really needed. However, if the same code were running in a paged ROM it would be vital.

The code itself is fairly straightforward.

The code at START gets the current memory layout and saves it to the stack, then sets the new layout in order to access ROM bank 2 and RAM bank 0, then it's another block move to copy the ROM into RAM.

The final lines restore the memory map from the stacked value and then exit.

## 4 THE VIDEO SYSTEM

The MTX series makes use of the TMS9929A Video Display Processor to generate the display in its PAL models, it was a popular device at the time and was used in a number of home computer systems. The NTSC equivalent is the TMS9928A. From a programmer's point of view, the 2 devices are very similar. The only major difference I'm aware of is because of the different television standard's frame rates, the VDP interrupt occurs 50 times a second on the PAL device and against 60 for NTSC.

The VDP has 16k of its own dedicated video memory, this memory is not visible to the Z80A CPU and all communication between the CPU and the VDP has to go via I/O ports.

The main advantages of the separate memory space means that the CPU does not have to give up RAM to the display nor is any extra circuitry needed to arbitrate between the CPU and VDP potentially slowing the CPU down.

The obvious disadvantage, the CPU has no direct access to the video memory reducing the rate at which new data can be moved to and from the screen. This is mitigated to a certain extent by the availability of hardware sprites and the choice of character mapped or bit mapped display modes.

The MTX ROM provides a number of useful routines for screen handling via the RST 10 and RST 28 interface. However, for maximum performance and some extra facilities, accessing the VDP directly is the way to go.

## 4.1 Accessing the Display via RST 10 and RST 28

The majority of the screen handling can be done via RST #10 and those functions are documented to a certain extent in the Phoenix manual as well as Keith's book. However, there are also a couple of useful routines within the functions of the general purpose RST #28 that I discovered from the ROM disassembly that I've not seen documented elsewhere.

Both RST #10 and #28 operate using in-line data. The RST instruction is followed by one or more data bytes. The program code then continues from the end for the data. Obviously, it is vital to get the data statements correct, otherwise a system crash is the likely result if the CPU starts trying to run data as program code.

RST 28 function #42 is used to initialize the video system and is called by the MTX ROM during start up. However, this is after the paged ROMs are set up, if you're programming a paged ROM, and need to do any printing then the following code is a must.

This calls the routine VDINIT at #2E85 in the Assem ROM, so there's no way to make the call directly from within a paged ROM. The other RST 28 function that can be used for accessing the display is function #AC (which calls the ROM routine PRINTX at #0CAB). This simply sends whatever is in the A register directly to the screen drivers. It will corrupt the A register on exit so should be used with that restriction in mind. It is however, faster to use than the equivalent RST 10 function.

Control codes, as well as displayable characters, can be sent to the display, as shown in the following example, which uses code 12 (clear screen) as well as 13 & 10 (carriage return and line feed)

```

10 ASSEM

CODE

0x4007

LD HL, DATA

0x400A LOOP:

LD A, (HL)

0x400B

AND A

0x400C

RET Z

0x400D

RST 28

0x400E

DB #AC

0x400F

INC HL

0x4010

JR LOOP

0x4012 DATA:

DB 12

DB "HELLO WORLD"

0x4013

0x401E

DB 13,10,0

0x4021

RET

Symbols:

DATA

4012 LOOP

400A

```

As the routine called by this RST 28 function is in the low ROM, it can be called directly, which is faster, but ends up being 1 byte longer. Since the function is called 14 times in the MTX ROMs, it would have saved the original programmers 14 bytes of ROM space. The RST and Data byte in the above code can be replaced with CALL #0CAB.

The RST 10 call is actually 4 functions accessed through one entry point. The bits 6 and 7 of the data byte determines which function is called. Bit 5 is the continuation bit if this is set then the RST 10 processing code expects to find another data byte after the completion of the current command. If it's clear the CPU will resume processing Z80 code at the end of the current command. Bits 0-4 of the data byte are command specific.

A data byte with the top 2 bits clear (i.e. 00 C xxxxx) are used to send a single byte to the display. As there are only 5 bits available, the value sent is restricted to between 0 and 31, which means control codes only. This may seem a little restrictive, but it is useful for things like clearing the screen or sending a carriage return to the display, as it is both shorter than any of the other options and needs no registers.

Sending a clear screen command (Character code 12 or #0C in hex) to the screen could be done with:

```

LD A,#0C

RST 28

DB #AC

```

Take twice as much space as:

```

RST 10

DB #0C

```

And changes the A register in the process.

Sending a carriage return and line feed to the screen can be done in 3 bytes:

```

RST 10

DB #2D,#0A

```

Note the setting of the continuation bit in the first data byte. There is no limit to the number of continuation items that form a single RST 10 command, nor are there any restrictions in mixing the various functions.

Data bytes with bit 7 clear and bit 6 set deal with the MTX's virtual screen system. Bit 5 is the continuation bit as with all commands, bit 4 isn't used. Bit 3 if set to 1 will clear the virtual screen, set to zero, it won't. Bits 0-2 are the virtual screen number 0-7.

For example, to select VS 4, clear it, and set the continuation bit ready for further printing, the bit pattern for the data byte would need to be  $01\ 1\ x\ 1\ 100$  which is #6C in hex (or #7C). Similarly, selecting VS 5 without clearing it and resuming processing, the data byte is  $01\ 0\ x\ 0\ 101$  or #45.

```

10 CODE

4007 RST 10

4008 DB #4C

4009 RET

Symbols:

20 PRINT "HELLO"

30 LINE 0,183,36,183

40 GOTO 40

```

This code the short assembly section selects VS 4, the graphics screen and clears it. The BASIC lines below print the message and underline it, producing the following output.

It also illustrates the fact that the display system treats all video data in the same way, whether it originates from BASIC or code.

The third function is the most complex, and also the most useful. The data byte has bit 7 set, bit 6 clear, and bit 5 is the continuation bit. The remaining 5 bits are a count from 1 to 31 of the number of bytes to be sent to the screen. Control codes and printable characters can be mixed as required, if more than 31 characters are needed, then the data can be separated into smaller sections and the continuation bit used.

To duplicate the above display with RST 10 the following code could be used.

```

10 CODE

4007 RST 10

4008 DB #6C

4009 DB #A7,"HELLO",13,10

4011 DB #85,2,0,183,36,183

4017 RET

Symbols:

```

The continuation bit is set on the command to select screen 4 and clear it, changing it from #4C to #6C. The next line is the 10 1 bit pattern for embedded data with the continuation bit set, as there are 7 data bytes following which is 00111, making the final byte #A7. The text that follows is the same as the BASIC, along with a carriage return and line feed.

The final line #85 is the bit pattern is 10 0 for embedded data and no continuation and 00101 indicating it is followed by 5 data bytes. The 5 data bytes are 2 which is the control code for LINE, followed by the same 4 positional bytes as the BASIC.

The final RST 10 function has both bits 6 and 7 set with bit 5 as the continuation bit as usual. The other 5 bits are unused. This function simply sends the 2 characters in the Z80's BC register pair to the screen. The Character in C is sent first, followed by B. The ROM actually uses RST 28 function #AC to do this. So, unless there is a compelling reason, in most cases it is probably simpler to use the RST 28 function. It saves having to remember which order BC is sent, and uses the A register which is probably more natural in most circumstances.

## 4.2 Accessing the VDP directly

Communication between the Z80 and the VDP is done using 2 I/O ports. Port 1 is used to transfer any data between the two, while port 2 is used by the Z80 to write to the VDP registers and memory pointer. Reading port 2 will access the VDP status register.

That's a little vague, so needs a little detail on exactly what that means.

The VDP has 16k of video memory connected to it, the Z80 only has indirect access to that memory. In order to place data into that memory, or read from it, it has to tell the VDP the address where it wants to access. Once that address is set up, each access to the data register will automatically increment the address pointer.

However, the VDP needs to know in advance whether the access through the data register at port 1 will be a read or a write. It's not possible, when say plotting a single pixel onto the bitmap display, to read a byte, set the pixel and write it back without doing a second address set up in between.

16k of RAM needs a 14-bit address to access each byte individually. Using 2, 8-bit, transfers leaves 2 bits for identification of the type of transfer taking place. The VDP uses bits 6 and 7 of the 2<sup>nd</sup> byte transferred for this.

In order to send a byte to the VDP RAM, the low 8 bits of the address need to be sent to port 2, followed by the upper 6 bits. Bit 7 of the 2<sup>nd</sup> byte needs to be a 0, bit 6 needs to be a 1. Any data then set to port 1 will be placed into the video RAM.

There are 2 potential issues with accessing the video memory this way. The first is that when your code starts an address set up its impossible to know whether the VDP is part way through an aborted address set up or not. The first byte you send could be completing a previous address set up. The solution is simply to read form either the data register on port 1 or the VDP status register on port 2 before starting the address set up.

The other issue is interrupts. It's possible for an interrupt to fire between the 2 VDP address setups. If that interrupt were to read the VDP status register, then the address setup would be re-started on return to your code with unpredictable results especially so on VDP writes. Unless you can be 100% certain that any interrupts won't access the VDP, or if you only access the VDP under interrupt control. Then a DI instruction before the address setup and an EI afterwards to temporarily halt interrupts can be a good idea.

It IS possible to write to the VDP from BASIC using the OUT command, and most of the time it will probably work as expected. But it's not guaranteed.

Port 2 is also used to write to any of the 8 VDP registers that control how the device is set up and what each section of video memory is used for. Register's 0 and 1 control the basic setup, which screen mode, sprites, the VDP interrupt etc. The Register 7 controls the colour of the backdrop and text screen. The other 5 registers are pointers to the various lookup tables the VDP uses to create the display.

There are timing restrictions with communicating with the VDP. After setting up the address, the CPU needs to wait 3 micro seconds before attempting to read or write data. With the MTX's Z80 running at 4mhz, this means the delay should be 12 machine cycles. This isn't a major issue, reading the data register with IN A,(1) takes 11 cycles, adding one instruction between the final address set up OUT (2),A and the IN instruction is sufficient. The same applies for writing to the data register as OUT (1),A also takes 11 cycles. There are other I/O instructions available on the Z80, however, they all take more cycles to complete.

What does need a little care is allowing sufficient time between successive data accesses in graphics modes. In text mode there's no problem the minimum time between read or writes is 2 micro seconds, which Is 8 cycles and all the I/O instructions take longer than that. In Graphics mode where the VDP needs more memory access for itself because of the complexity of the display, 8 micro seconds are required between CPU accesses, so a little thought is required when laying out screen access code.

Which mode the VDP is using, is determined by the current setup, and that requires writing to one or more of the 8 write only registers.

In order to write to a register, the register data is sent to port 2 first, then the register number, to separate register writes from the address set up sequence Bit 7 should be set, and bit 6 should be clear. The register number should be between 0 and 7 to maintain compatibility.

Register 0 and 1 between them can best be thought of as a collection flags.

| Register | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | BIT 1 | Bit 0 |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0        |       |       |       |       |       |       | M3    | EV    |

| 1        | 4/16k | Blank | IE    | M1    | M2    |       | Size  | Mag   |

7 of the 16 bits are un-used and should be set to 0 for compatibility with later VDPs. Of the remaining 9, M1, M2 and M3 select which display mode the VDP uses. None of the modes require more than one bit to be set. It is possible to create "illegal" screen modes by setting more than one mode bit, those modes aren't documented here.

The first 3 modes were inherited from the older TMS9918 VDP used in the TI 99/4. Graphics 2 is only available on the later "A" version devices. (9918A, 9928A and 9929A)

With all 3 bits clear, the VDP will be in graphics 1 mode. The display is 32 by 24 in up to 15 colours, the sprites system is active. Each character can only have 2 colours.

M1 set, M2 and M3 clear puts the VDP into text mode. The display is set to 40 by 24 in 2 colours and the sprite system is turned off. There are 2 colours available for the whole display, setting individual character colours is not possible

M2 set, M1 and M3 clear puts the VDP into Multi colour mode, the display is 64 by 48 in 15 colours, sprites are active. I'm not aware of any MTX software that uses this mode.

M3 set, M1 and M2 clear puts the VDP into Graphics 2 mode, The Display is 32 by 24 in up to 15 colours. Each character row has its own 2 colours, with the correct setup a bitmapped display can be created.

There's only one other useable bit in register 0, EV. Setting this bit enables the external video input in the 9918 and 9918A. Since the MTX uses the 9929A setting it has no effect, and so it should be set to 0 for compatibility.

Register 1 has 5 other, useable bits. Bit 7 should be set on the MTX, as it's used to inform the VDP of the amount of video RAM fitted. With the bit clear the VDP will assume 4k x1 RAM chips are fitted and adjust accordingly.

If the BLANK bit is clear, then the VDP display is turned off, and will show the current border/backdrop colour. Setting it to 1 restores the current display, so possibly of use in some circumstances to hide the display being built.

The IE bit, is the interrupt enable, if this is set the VDP will issue an interrupt at the end of the active display. The interrupt signal from the VDP is connected to the input of counter/timer 0 on the CTC, meaning both the CTC and VDP need to be correctly setup in order to make use of the VDP interrupt. Although its connected to the CTC, the MTX ROMs make no use of the video interrupt. If VDP interrupts are used, the VDP status register must be read during the interrupt routine as reading the register clears the interrupt flag. If the interrupt flag isn't cleared further interrupts can't occur.

Bits 0 and 1 control the sprite settings. If MAG is set, all sprites are drawn double size. If the Size bit is set, then sprites are drawn from 4 consecutive 8x8 sprite characters in memory. If unset, then 8x8 sprites are drawn from a single sprite character.

At reset, the VDP sets both register 0 and 1 to all zero, meaning the display is blanked, interrupts are off and the VDP is in graphics 1 mode with 8x8 single pixel sprites.

| The remaining  | 6 registers  | have the | following     | functions       |

|----------------|--------------|----------|---------------|-----------------|

| THE TELLIGIBLE | 0 1 05131013 | Have the | TO HO VVIII E | i di i ctionis. |

| Register | Function               | Bit 7                  | Bit 6 | Bit 5 | Bit 4  | BIT 3   | BIT 2     | BIT 1 | BIT 0 |

|----------|------------------------|------------------------|-------|-------|--------|---------|-----------|-------|-------|

| 2        | Name Table             | 0                      | 0     | 0     | 0      | A13     | A12       | A11   | A10   |

| 3        | Colour Table           | A13                    | A12   | A11   | A10    | A9      | A8        | A7    | A6    |

| 4        | Pattern Table          | 0                      | 0     | 0     | 0      | 0       | A13       | A12   | A11   |

| 5        | Sprite Attribute Table | 0                      | A13   | A12   | A11    | A10     | A9        | A8    | A7    |

| 6        | Sprite Pattern Table   | 0                      | 0     | 0     | 0      | 0       | A13       | A12   | A11   |

| 7        | Text Colour Register   | Text Mode, Text Colour |       |       | Backgr | ound/Bo | rder colo | ur    |       |

Depending on the display mode some of the registers may not be used. As each table in video memory requires differing amounts of space depending on the amount of data it holds, the VDP designers decided to restrict the amount of address bits available to position the table. I.e. the "Name Table" is 1k in size, the programmer can position it on any kilobyte boundary as just 4 of the 8 bits in the register are used. As usual any un-used high order bits need to be set to 0 for compatibility with later devices.

It's important to note, that though the number of bits available for locating tables in video ram is restricted, overlapping of tables is allowed. For example, the Pattern Table and Sprite Pattern Table could occupy the same position in VRAM, with the programmer then deciding which sections of the table are used as characters, and which as sprites, or both!

The VDP is primarily a character-based device, and in order to create a character-based display 2 tables are required. The Name Table is in effect a character map for the display. So for example, if the display is set with the ASCII character set, placing a byte with a value of #41 (decimal 65) into the first entry in the table will display the character "A" on the top left of the screen.

The Pattern Table contains the actual character pattern that is displayed. There are 8 bytes per character, and 256 possible characters, making a maximum table size of 2k, which is why the register only allocates 3 bits for the pointer. The name table must go on a 2k boundary.

#### 4.3 Text Mode

Text mode uses 3 of the VDP registers to control the display. These are register 2 the name table, register 4, the pattern table and register 7 the colour register.

Only 2 colours are available, any "set" pixels will show as the text colour from the upper 4 bits of register 7, everything else is rendered in the backdrop colour from the lower 4 bits of the same register.

The ROM places the Pattern Table at #1800 in VRAM, with the Name table over lapping it at #1C00. This effectively reduces the pattern table to 128 or so entries, of which the ROM sets up patterns 32 to 127 as the ASCII character set. Pattern 0 is also used by the cursor.

The overlapping table setup is required to fit both the bitmap graphics display (I hesitate to call it High Resolution) and text mode into the available ram space without them interfering with each other.

In order to set the display, the MTX rom sends the following data to the 3 registers

```

Register 2: #07

Register 4: #03

Register 7: #F5

```

The binary version of the table pointer values makes it a little clearer what is being set:

```

Register 2; (0000) 01 1100 0000 0000 Register 4: (00000) 01 1000 0000 0000

```

The cleared upper bits (in brackets) are ignored by the 9929 VDP but should be programmed as clear for compatibility. Referring to the table above, for register 2 the lower 4 bits are significant, for register 4 it's only 3,. Adding in the rest of the low order address bits (in red) confirms that register 2 has set the name table to #1c00 and register 4 the pattern table to #1800.

Register 7 is much simpler to understand, as it's setting white text -colour 15 (f) on a light blue background -colour 5.

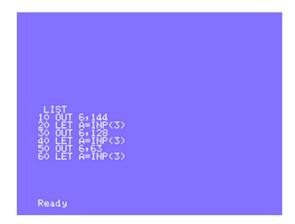

Unless there's a good reason not to, it's simpler to use the MTX's default VRAM layout than to define one of your own. The following BASIC program illustrates direct screen access

```

0 LET A=INP(2)

10 OUT 2,2*16+1

20 OUT 2,128+7

30 OUT 2,1

40 OUT 2,64+28

50 LET A$+"Hello World"

60 FOR X=1 TO LEN (A$)

70 OUT 1,ASC(MID$(A$,X,1))

80 NEXT

90 GOTO 90

```

```

Line 0 clears any part written port 2 setup.

Lines 10 and 20 set register 7 to #21, for a green on black display.

Line 30 and 40 set the VRAM pointer to #1C01 ready for writing

Line 50 is the message

Lines 60 to 80 pass that message 1 byte at a time to the video ram.

Line 90 prevents the MTX from reverting to blue on white when the program ends.

```

All characters and sprites used by the VDP are based on an 8 by 8 matrix, however on order to fit 40 columns on a display 256 pixels wide the lowest 2 bits of each row of character data are ignored. The 40 column display is therefore 240 pixels wide, to accommodate this the borders are adjusted to keep the screen more or less central.

Assuming the name table is at its default position at #1C00 the location of any character on the screen can be calculated as #1C00 + row \* 40 + column. An additional factor to take into account when writing to the screen is that bit 6 needs to be set on the address transfer, making the calculation effectively #5C00 + row \* 40 + column.

In assembler there are several ways to calculate this. The simplest is probably to use left shifts to multiply by 2. As 40 is 5 x 8, he following routine will calculate the screen address in HL, assuming the row number is in B and the column in C, B and C are assumed to have been range checked and so B is between 0 and 23 and C between 0 and 39. Multiplying B by 5 is done in the A register as  $5 \times 39$  is 235 and is with the permitted values for an 8 bit register. The final multiply by 8 needs a 16 bit register pair.

```

SCREEN POS:

PUSH AF

; save the working registers for neatness

PUSH BC

LD A, B

ADD A, A

; 2x row

; 4x row

ADD A, A

ADD A, B

; 5x row

LD L,A

; transfer A to HL for the final multiply by 8

LD H, 0

ADD HL, HL

; 10x row

; 20x row

ADD HL, HL

ADD HL, HL

; 40x row

LD B,#1C

; the column value is in C, setting B to #1C here

; saves having to add #1C00 later

```

```

ADD HL, BC

POP BC

POP AF

RET

```

Reading or writing the character ad row B, column C is then simply:

```

WRITE_A:

CALL SCREEN_POS

PUSH AF

LD A,L

OUT (2),A

LD A,H

OR #40

OUT (2),A

POP AF

OUT (1),A

RET

```

Reading the character is even simpler:

```

READ_A:

CALL SCREEN_POS

IN A, (1)

RET

```

Since the VDP's internal character pointer is incremented after each access, the further characters could be transferred with just an additional IN A,(1) or OUT (1),A.

To change the appearance of any character, simply update the data in the pattern table. Each character is stored as 8 consecutive bytes, in the default setup, the position is therefore #1800 + 8 \* character\_no

To set HL to the location of character A one way of doing it is:

```

CHARCTER_POS:

LD L,A ; character code can be any value 0-255

LD H,3 ; save adding #1800 later, by adding #0300 now

ADD HL,HL ; HL is now #0600 + 2 x A

ADD HL,HL ; HL is now #0C00 + 4 x A

ADD HL,HL ; HL is now #1800 + 8 X A

RET

```

Once the VDP address pointer is set up, then 8 bytes can be transferred with repeated IN or OUT instructions.

I mentioned earlier that there overlapping of the table leaves approximately 128 characters available to the programmer, provided the cursor blink is accounted for, Entries character codes 0-127 are free, then next 960 bytes are taken up by the name table, this leaved a further 64 bytes at the end of the name table that can be used for character definitions. That makes 8 further characters with codes 248 to 255 that can be defined without corrupting the display, making 136 in all.

#### 4.4 GRAPHICS 2 MODE

Graphics 2 is the other mode used as standard on the MTX, despite appearances, it is a character-based mode. In G2 mode there are 24 rows of 32 columns in the display, giving 768 locations. However, with the normal G2 setup, the name, pattern and colour tables are both split into thirds, each third of the name table therefore has 256 entries, allowing each one to be unique. Each byte in the Pattern table has a corresponding byte in the colour table, allowing each group of 8 pixels to have 2 colours.

In order to use the display as if it were bitmapped, each segment of the name table is set up as ascending bytes from 0 to 255 (#FF). The display is then created by accessing the pattern and colour tables directly.

In G2 mode the name table is 768 bytes, making the Pattern table 768 x8, or 6144 bytes in length, as is the colour table. Therefore, there are only 2 possible locations for these tables. Right at the start of Vram in locations 0 -6143 (#17FF) or from the mid-point from 8192 to 14335 (#2000-#37FF).

The Pattern Table and Colour table meanings are modified, only the A13 has any significance in determining the table location. The TI documentation says that all the lower order address bits need to be set to 1 in order to use the full number of patterns. This gives the following 4 "legal" values for the 2 tables

| Table   | Register | Binary     | Decimal | Hex | Decimal      | Hex Location  |             |

|---------|----------|------------|---------|-----|--------------|---------------|-------------|

|         |          | Value      |         |     | Location     |               |             |

| Pattern | 4        | 00000 0 11 | 3       | #03 | 0 - 6143     | #0000 - #17FF | MTX setting |

| Pattern | 4        | 00000 1 11 | 7       | #07 | 8192 - 14335 | #2000 - #37FF |             |

| Colour  | 3        | 0 1111111  | 127     | #7F | 0 - 6143     | #0000 - #17FF |             |

| Colour  | 3        | 1 1111111  | 255     | #FF | 8192 - 14335 | #2000 - #37FF | MTX setting |

To avoid complications with overlapping tables, the name table needs to be fitted into one of the available 2k blocks. The MTX rom uses the first "free" area for the text screen, so places the sprites and Name table in the 2<sup>nd</sup> area. Register 2 is set to 15 (#0f) placing the table at 15386 (#3C00) however once it's set up it can be forgotten.

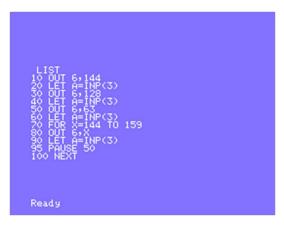

The following BASIC code is an example of how to setup and access graphics 2.

```

O REM GRAPHIC 2 SETUP EXAMPLE

10 LET A=INP(2)

20 OUT 2,3: OUT 2,128+4

30 OUT 2,255; OUT 2,128+3

40 OUT 2,15; OUT 2,128+2

50 OUT 2,15: OUT 2,128+7

60 OUT 2,0: OUT 2,64+60

70 FOR X=1 TO 3

80 FOR Y=0 TO 255

90 OUT 1,Y

100 NEXT

110 NEXT

120 OUT 2,2: OUT 2,128+0

130 OUT 2,64: OUT 2,128+1

```

```

140 OUT 2,0: OUT 2,64+0

150 FOR X=0 TO 6143

160 OUT 1,85

170 NEXT

180 OUT 2,0: OUT 2,64+32

190 FOR X=0 TO 6143

200 OUT 1,INT(X/24)

210 NEXT X

999 GOTO 999

```

The code can be broken down into 2 sections, first the setup sequence:

Line 10 is there to clear any part started transfers. Lines 2- to 40 set up the pattern table, colour table and name table with the MTX default values. Line 50 sets the border to white. Lines 70 to 110 then set up the name table as the required 3 repeating sequences of 0 to 255. Lines 120 and 130 set up the required mode bits for graphic 2, and turn on the display.

The second section sets up a display. Line 140 sets the video memory pointer to the start of the pattern table which is at locations 0 to 6143. The +64 is to ensure the VDP is expecting memory writes. Lines 150 to 170 then poke a vertical line pattern into the screen memory. Line 180 then moves the video memory pointer to 8192 (#2000), again setting up for transfers to vram. Lines 190 to 210 then set 24 consecutive locations (3 characters) to each of the 256 possible colour combinations.

Line 999 is just there to stop BASIC returning to "Ready" on completion.

For a checkerboard display instead of lines, add the following

```

145 LET J=85

160 OUT 1,J

165 LET J=255-J

```

Because the display is character mapped, calculating the screen address is more complicated that it would be if it were arranged on a row by row basis. It's best explained using the binary representation of the values. As each row of the character is 8 pixels wide, and each character fills 8 rows, the "x" value can be thought of as 2 fields. The upper most 5 bits select which column of characters to access, the 3 x bits, determine which pixel within the character row. The first pixel within the byte that's displayed being bit 7, so the bit order needs to be reversed, as bi7 7 is pixel 0, bit 6 pixel 1 etc.

Each character is 8 rows high, so the 3 low bits of the Y value select this offset into the character. As each group of 8 rows is 256 bytes long (8 rows x 32 characters) the upper 5 bits determine the high byte of the address.

Colour memory is grouped by 8 pixels, so the calculation is identical except the 3 low "x" bits are ignored, and the offset for colour memory has to be added.

Binary representation of the X value (0-255) cccc xxx

Binary representation of the Y Value (0-191) rrrrr yyy

Final pixel address 000rrrrrcccccyyy, bit 7-xxx

Final colour address 001rrrrrcccccyyy

Drawing a line in BASIC could be done something like this:

```

10 REM GRAPHICS 2 PLOTTING

20 VS 4

30 CLS

40 FOR YPOS=0 TO 191

50 LET XPOS=INT(50+ypos/2)

60 LET C=8*INT(XPOS/8)

70 LET B=7-(XPOS-C)

80 LET R=INT(YPOS/8)

90 LET Y=YPOS-8*R

100 REM PLOT IT!

110 OUT 2,C+Y: OUT 2,64+R: OUT 1,2^B

120 NEXT

999 GOTO 999

```

NB BASIC's OUT command is sufficiently slow the line is almost guaranteed to have glitches!

The equivalent code in assembler is actually a little easier to follow because of the CPU's ability to mask bits in a way BASIC doesn't provide

Assuming on input the B register holds the X position, and the C register the Y one. The following code will set up HL with the byte address.

```

LD A, 7

; mask for the lowest 3 bits

; A is now the low 3 bits of the Y value only (yyy)

AND C

LD L,A

; save for later

LD A, \#248; mask for the top 5 bits

AND B ; A is now the top 5 bits of the x value (cccc000)

OR L

; add back the stored value

LD L, A

; the low byte is now cccccyyy as above

; get the Y value

LD H,C

; shift right 3 places to form

SRL H

SRL H

; 000rrrrr

SRL H

; HL now has the full address 000rrrrrcccccyyy

```

There's a major issue that still needs to be dealt with, the code above over writes all 8 pixels in the byte to set just the one. What needs to happen is first read in the byte from screen memory, set the pixel and then write it back. However, the screen memory pointer needs to know in advance the type of access being done and it also auto increments after the read, so the address needs to be set up again for the write back. Which leads to the following sequence:

```

Calculate the screen address

Set up the screen address, for a reading

Read the byte

set/reset the required pixel

set up the screen address for writing

write back the modified byte

set up the screen address + #2000 also for writing

write the colour data

```

And that all takes time.

#### 4.4.1 Graphics 2 in text mode

While MTX BASIC uses Graphics 2 as a bitmapped display, the underlying display system is actually a character based one.

Using it as a text display is not unlike the 40 column text mode, the display is 32 characters by 24. Using the default screen set up, the character and colour data needs to be written 3 times, to each of the pattern and colour tables.

Once that is done, a single byte update to the name table updates the display, and unlike the default MTX setup for text mode, all 256 patterns are available.

There is a simpler way to achieve the same effect using some less well documented abilities of the VDP. The TI documentation advises that the "unused" low bits of the pattern and name tables should be set to 1. The reason for this is that those bits are binary ANDed with the memory address when accessing video memory.

Bit 2 selects which of the two 8k halves of the video memory are used for the Pattern table. That is bit A13 of the video memory address, bits 0 and 1 therefore will mask A11 and A12 respectively. Using the default setup both those bits are set to 1, and the full memory range is accessed. However, if they are both set to 0 along with bit 2, all video memory reads for the pattern table will be from the first 2k table only.

From BASIC this can be demonstrated with

```

10 VS 4: CLS

20 PRINT "COMPRESSED PATTERN TABLE"

30 OUT 2,0: OUT 2,128+4

40 GOTO 40

```

Line 30 here sets VDP register 4 to 0, forcing the VDP to use the first table for all 3 segments of the screen. Resulting in the text appearing on the screen 3 times, in the top row of each 1/3 of the screen.

For the colour table, bit 7 of register 3 sets the upper or lower bank, leaving bits 5 and 6 to mask A11 and A12. Masking lower bits will reduce the colour table further but don't really add anything to the flexibility of the compressed display. Clearing bits 5 and 6 gives a binary pattern of 1001 1111, which is #9F in hex and 159 in decimal.

Changing the default VDP setup this way means that there is effectively one 2k long table in video memory at #0000 to #1FFF for the character patterns and one 2k long table at #8000 to #9FFF for the colours. The table at #3C00 to 3EFF is then the character map for the display.

#### Using BASIC to demonstrate:

```

10 VS 4: CLS

20 CSR 0,1

30 OUT 2,0: OUT 2,128+4

40 OUT 2,159: OUT 2,128+3

50 FOR X=32 TO 126

60 PRINT CHR$(X);

70 NEXT X

80 OUT 2,0: OUT 2,64+60

90 FOR X=0 TO 767

100 OUT 1,32

110 NEXT X

120 OUT 2,0: OUT 2,64+60

130 LET A$= "G2 TEXT MODE DISPLAY"

140 FOR X= 1 TO LEN (A$)

150 OUT 1, ASC (A$(X))

160 NEXT X

170 GOTO 170

```

The section up to line 70, sets up the display, and pokes the standard MTX character set into the definitions for characters 32 to 126.

Line 80 then sets the video memory output pointer to #3C00, then 90 to 110 clear the screen by inserting spaces.

Line 120 then sets the pointer back to the top of the screen for line 130 onwards to output the text in A\$ to the display.

Adding the following will show that the colours are defined per character, and not for the whole display as is the case for text mode.

```

55 COLOUR 0,1+RND*15

```

Leaving out one of line 30 or 40 will map one table to 2k and the other to the default 6k allowing for either one set of characters with 3 sets of colours one for each 1/3 of the screen, or the reverse where there are separate characters for each 1/3, but only one set of colours.

## 5 THE CTC

The MTX uses the standard Z80A CTC to handle the Clocks for the optional RS232 board and cassette tape interface as well as the main system timer. The CTC in the device name highlight that it is both a Counter and Timer Chip.

There are 4 "event" inputs on the CTC. The VDP interrupt is connected to the channel 0 input, but isn't used by the OS, channels 1 and 2 are the master baud rate clock inputs and are both connected to a 300kHz clock obtained by dividing the main system clock by 13. The final input on channel 3 is the feed from the tape input circuitry.

Due to package limitations, the CTC only has 3 outputs instead of the expected 4. Channel 0 is unconnected, while channels 1 and 2 feed out to the edge connectors as the SER1 and SER2 signals for the RS232 board

Neither of the MTX manuals goes into great detail on the CTC, however with the Zilog datasheet being readily available on the net, that's not as much of issue as it might have been in the 80s.

The CTC occupies 4 read/write I/O ports in the MTX running from #08 to #0B (8 to 11 decimal). The CTC also needs 8 bytes of RAM for an interrupt vector table so that each counter/timer can have its own interrupt routine. That table is stored right at the top of memory at #FFFO (65520 decimal).

Each channel has 2 registers, the channel control word and time constant word. There's also an additional "common" register, the interrupt vector word.

| Register  | Bit 7     | Bit 6   | Bit 5     | Bit 4  | Bit 3   | Bit 2    | BIT 1    | Bit 0 |

|-----------|-----------|---------|-----------|--------|---------|----------|----------|-------|

| Interrupt | A7        | A6      | A5        | A4     | A3      | xx       | xx       | 0     |

| Vector    |           |         |           |        |         |          |          |       |

| Channel   | Interrupt | Channel | Prescaler | Edge   | Timer   | Time     | Software | 1     |

| Control   | Enable    | Mode    | Mode      | Select | Trigger | Constant | Reset    |       |

|           |           |         |           |        |         | Follows  |          |       |

The MTX sets up the CTC at #097F in the main OS rom and can be viewed in Panel.

The interrupt vector is set in 2 steps. The Z80's I register needs to be set to #FF to set the top byte. The CTC interrupt vector word is set to #F0 to provide the remainder of the base address, bit 0 being clear informs the CTC this is a vector word.

Next all 4 channels are reset in software. Before the routine ends.

## 5.1 125HZ INTERRUPT

Unlike most systems the main interrupt runs at 125Hz and not anything related to the screen refresh rate. This has the obvious advantage that the interrupt will run at the same speed on all systems regardless of the VDP fitted. That removes the need for separate NTSC and PAL versions of the ROM.

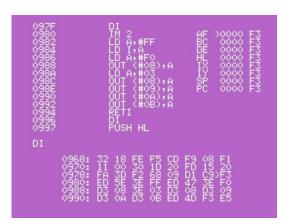

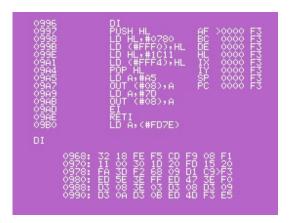

The setup code of the interrupt is at #0996 in the OS ROM

This sets up 2 of the 4 interrupt vectors, Channel 0 at #FFF0 is set to #0780 which interestingly the MTX source labels to as vdpint and channel 2 at #FFF4 is set to #1C11 which is referred to as enter in the original sources.

The channel control word for channel 0 is set to #A5 which translates to 10100101 in binary.

Bit 7 set: Enable Channel 0 interrupt

Bit 6 clear: Timer mode – ie controlled from the 4mhz clock, and not the channel 0 input pin

Bit 5 set: Pre-scale value is 256

Bit 4 clear: Falling edge controlled

Bit 3 clear: Automatic trigger when the time constant loads

Bit 2 set: Time constant follows next

Bit 1 clear: No channel reset

Bit 0 set: This is a control word update

The main clock is 4MHz, divided by the 256 pre-scale value results in a counting rate of 15625 counts per second. The time constant that follows is 7D (125 decimal) 15625 divided by 125 results in the final 125Hz interrupt which vectors to #0780

The channel 2 interrupt isn't set up, even though the CTC setup code has put it into the vector table.

#### 5.1.1 So why 125Hz?

That's probably because the CTC cannot produce any integer interrupt rates that are lower than that when running from the 4MHz main clock. Using a fractional rate isn't really practical when updating the system clock.

## 5.1.2 MTX BASIC and Interrupts

The MTX ROMs update the master clock on every interrupt in the routine "vdpint" at #0780. The last byte of the CLOCK system variable at #FD5D is incremented every "tick" from counting up from 48 to 173. The 6 bytes that form the data for CLOCK and TIME\$ are updated when that counter hits 173. The count starts at 48 as that's ASCII code for a zero, and the remainder of the clock counts in ASCII to simplify the code required to set and read the clock in BASIC.

Once the clock is dealt with the system variable INTFFF at checked so that the main interrupt code is only run on alternate "ticks" which results in BASIC being a little more responsive as the longer codes sequence is only run 62.5 times a second on average.

If the interrupt code is run, INTFFF is used as a mask to determine which of 5 possible interrupt routines are called.

- Bit 0: If set enables the interrupt driven sound

- Bit 1: If set enables the break key check

- Bit 2: If set enabled the keyboard repeat

- Bit 3: If set enables cursor flash and Sprite movement

- Bit 4: If set enables a call through USERINT at #FA98

- Bit 5: If set enables a call through USERINT at #FA98

- Bit 6: If set enables a call through USERINT at #FA98

- Bit 7: If set tells the system to bypass the interrupt system this time around.

If more than one of bits 4 5 and 6 are set, the USERINT will be called once for each bit.

A BASIC program that runs in text mode, with no sound can run a around 3% faster if 64862 is poked with 6. For a game that doesn't want the break key operative, then poke in a 13 instead.

## 5.2 BAUD RATE CLOCKS

The CTC delegates 2 of the 3 active inputs to the baud rate counter.

The master clock for this is 4MHz divided by 13 using ap 74LS193 on the motherboard, which results in a not quite square wave at 307.7kHz (the signal is low for 2000 ns but only high for 1250).

The BAUD command from BASIC then programs the CTC to count those pulses. The baud rate table is stored in rom at #0CFA and defines 10 speeds from 19200 baud down to 75 baud. Each entry is 3 bytes, 2 bytes for the baud rate in binary, followed by the divider value to program into the CTC.

19200 baud is the fastest rate than can be achieved, and is the result of dividing the 307.7kHz input clock with the 16 count pre-scale and triggering on every pulse. The lowest rate of 75 baud requires the maximum 256 counter value with the 16 count pre-scale.

4,000,000 / 13 / 16 gives an output rate of 19231Hz, which is close enough to 19200 not to cause any communications issues. To get a "perfect 19200 would require the input clock to be 307.2kHz, which isn't possible for a 4MHz main clock.

The output from the CTC on SERO and SER1 is nothing like a square wave, the output is only low for 1 period of the 307.7kHz clock however that's enough to clock the Z80 Dart on the communications board.

## 5.3 VDP INTERRUPT

While the VDP interrupt isn't used by the MTX roms, it is connected to the highest priority input on the CTC. So games, and anything else that takes over the whole system can synchronise themselves to the VDP in order to use the horizontal blanking period for smooth screen updates.

What it needs is the CTC to be set to count pulses on channel 0, with a count of 1 so that every VDP interrupt trigger a CTC interrupt. The interrupt pointer at #FFF0 will then be called 50 or 60 times a second, depending on the VDP fitted.

## 5.4 INTERRUPT PRIORITY

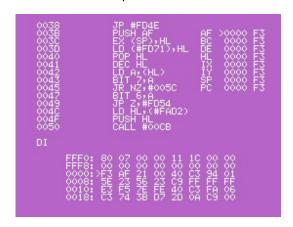

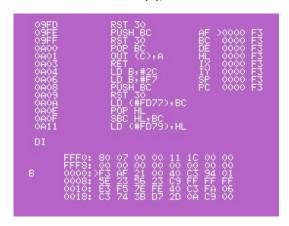

The Z80 has 2 interrupt sources IRQ and NMI pins. IRQ or interrupt request is the only one used by the MTX. The higher priority NMI isn't used.

The IRQ system has 3 modes of operation, mode 0 which is 8080 compatible, mode 1 which vectors all interrupts through address #0038 and mode 2 which allows Z80 peripherals to supply an automatic vector address

The MTX uses mode 2. Support has been built into the rom for mode 1 operation. Code at #0038 jumps to the system variables at #FD4E which is labelled USRRST. By default, that in turn jumps to a routine called enter30 in the source at #1C03 which drops into Panel.

If an NMI is triggered by external hardware, the "support" provided by the rom is to issue the RST#38 instruction and call the code above.

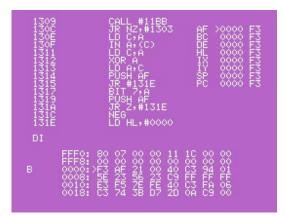

```

0056 RST 38

0067 LD HL;#00FC AF >0000 F3

006A AND #3F BC 0000 F3

006C CALL #0689 DE 0000 F3

005F PUSH HL HL 0000 F3

0073 PUSH HL IY 0000 F3

0074 PUSH HL IY 0000 F3

0074 PUSH HL OF SP 0000 F3

0075 LD HL;(#FD6F) PC 0000 F3

0078 RET

0079 PUSH HL

007A LD HL;(#FAD2)

007B LD HL;(#FAD2)

007C AND #8F

DI

FFF0: 80 07 00 00 11 1C 00 00

FFF8: 00 00 00 00 00 00 00

0000: F3 AF 21 00 40 C3 94 01

0008: 5E 23 56 23 C9 FF FF FF

0010: E3 F5 7E FE 40 C3 FA 06

0018: C3 74 3B D7 2D 0A C9 00

```

There is a bit of a "gottcha" with this. Because RST #38 is a call and not a jump, it puts the return address on the stack. Any user routine that intercepts the jump through USRRST will need to remember to adjust the stack on exit otherwise the RETN will "return" control to #0067 instead of the real location.

The Z80 is designed so that there is an "chain" of devices that may issue IRQ interrupts to the CPU. The CTC is wired as the first device in that chain. Its interrupt will always have priority over any other device on the chain. Z80 peripheral chips have an interrupt enable in (IEI) and interrupt enable out (IEO) pin.

The IEI signal has to be high for an interrupt to occur. The IEI for the CTC is connected to the 5v rail through a resistor and is always high.

The IEO signal will be pulled low while the CTC is servicing an interrupt, any devices further down the chain will only issue an interrupt if their IEI pin is high. If their IEI pin is low, they set their own IEO pin low to maintain the integrity of the chain.

If there are too many devices (typically more than 3) on the chain, the time taken for the IEO to traverse the chain can cause issues, that's not a problem with the MTX as the standard system only has the CTC on the chain. With the RS232 board connected the DART will also be on the chain.

## 6 THE PSG

The MTX uses the 4 channel Texas Instruments SN76489A Programmable sound Generator. The A version indicates it's the later 4MHz capable version. The PSG was used in a number of systems in the late 70's early 80 most notably in the BBC Micro. The PSG mono device so although the MTX has a "HiFi" port on the back, it's only a single channel, and not stereo.

The chip itself is relatively slow as it's basically a 500kHz device (The original SN76489 with a divide by 8 on the clock input.) and needs 32 cycles at 4mhz to complete a read of the data bus. Rather than hold up the CPU while the data is transferred, Memotech devised a hardware solution that doesn't use "ready" from the sound chip to pause the CPU.

Instead OUT (6),data writes to a 74LS374 8 bit latch. IN A,(3) then starts the PSG data read from the latch. The Data returned from reading port 3 is irrelevant, it's the action of reading the port that starts the access, there's actually no valid data being output at that point in time to read.

Since the PSG is reading from the latch it can take as much time as it needs, the CPU is then free to carry on processing. The manual warns that there should be at least 32 T states (or CPU cycles) between reads. That's not quite accurate, there needs to be 32 T states between the IN (3) and the next OUT (6). If the data in the latch is updated before the PSG completes the read, the data is corrupted.

The MTX ROMs have a routine at #093A (2362 decimal) to turn off all 4 sound channels. Calling #0953 (2387 decimal) will sound the bell, without needing to go through the overhead of using the VDU routines.

## 6.1 PSG REGISTERS

The PSG has 8 internal registers, each of the 4 channels has its own volume and frequency register. Internally the volume is stored in 4 bits, and the frequency counter in 10 bits. The nose channel treats the received data differently from the 3 tone channels but the update method is the same.

The data sheet refers to one and 2 byte data transfers, with a 2 byte transfer to update the frequency registers and a one byte transfer to update the noise and volume registers. Because of the way that the PSG latches the channel information the frequency can also be updated with a one byte update.

Which part of a PSG update is in progress depends on bit 7 of the data byte sent to port 6.

|                  | Bit 7 | Bit 6         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------|-------|---------------|-------|-------|-------|-------|-------|-------|

|                  |       |               |       |       |       |       |       |       |

| Frequency update | 0     | Don't<br>care | F9    | F8    | F7    | F6    | F5    | F4    |

| Source update    | 1     | Ch1           | Ch0   | D/V   | X3    | X2    | X1    | X0    |

If bit 7 is high indicating a source update the PSG will latch the 2 channel bits and the D/V bit, and then sent the 4 low bits to the appropriate internal register.

| Channel bits | Destination Channel |

|--------------|---------------------|

| 00           | Tone 1              |

| 01           | Tone 2              |

| 10           | Tone 3              |

| 11           | Noise Generator     |

If the D/V bit is low, then the destination is the frequency, if it's high the volume register is selected. The 4 low bits then set the low 4 bits of the frequency count or the volume.

The volume control actually works in reverse, the 4 bis control the amount of attenuation of the signal. So, 0 is maximum volume and 15 turns that channel off.